- 全部

- 默认排序

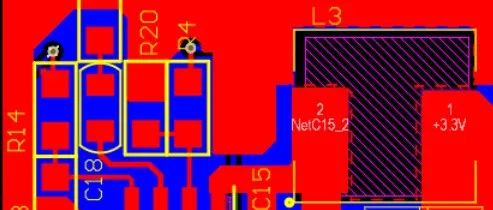

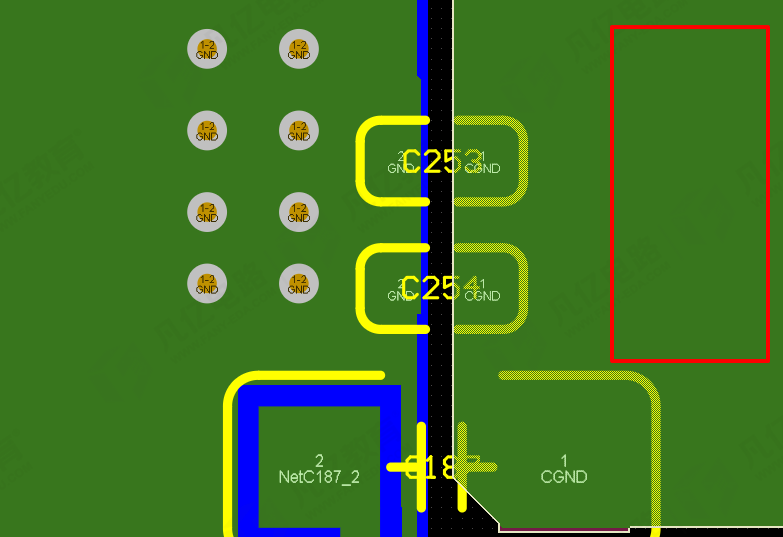

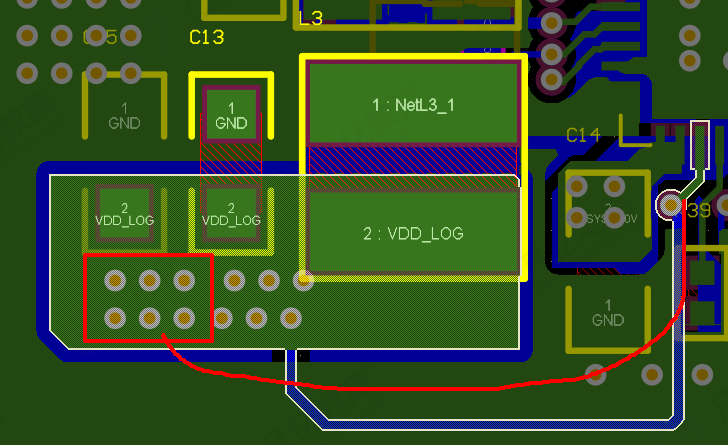

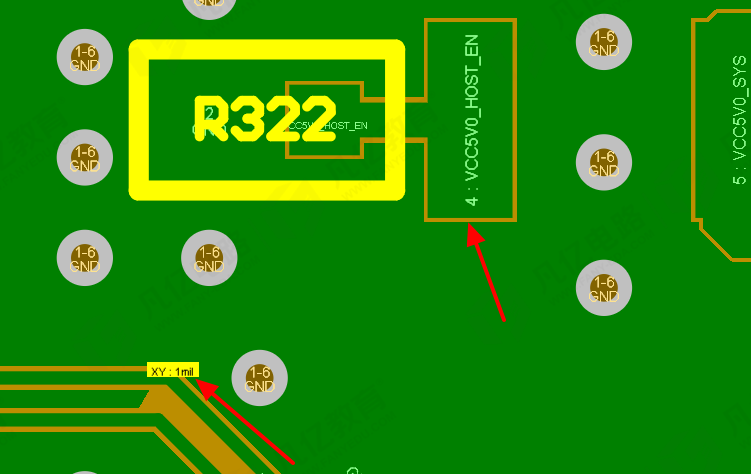

1.线宽要保持一致,线宽不一致会导致阻抗不连续。2.TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空 间的情况下,包地处理。3.数据线等长错误,避免绕90度角等长。4.铺铜存在多处孤岛铜和尖岬铜皮以上评审报告来源于凡亿教育90天

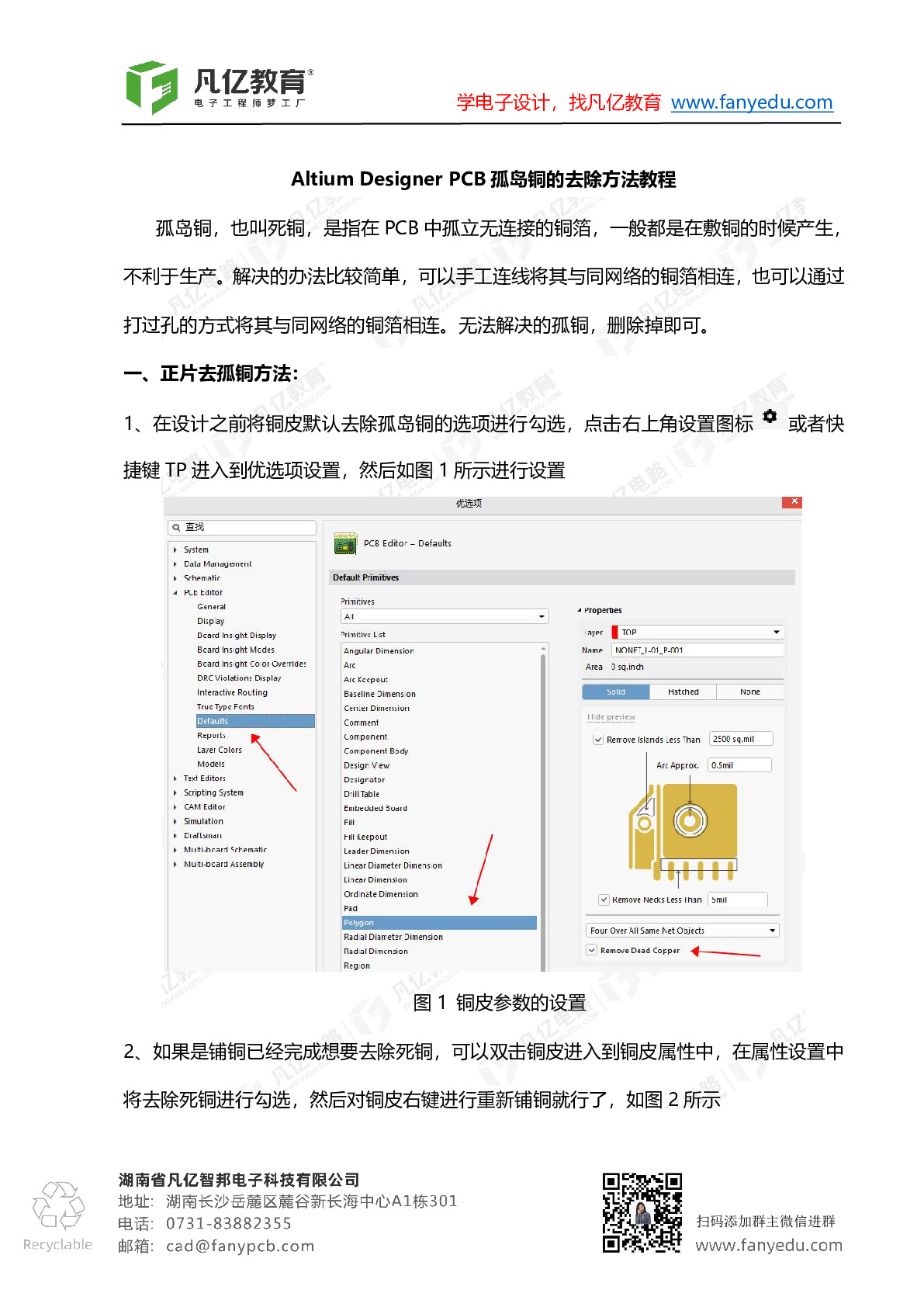

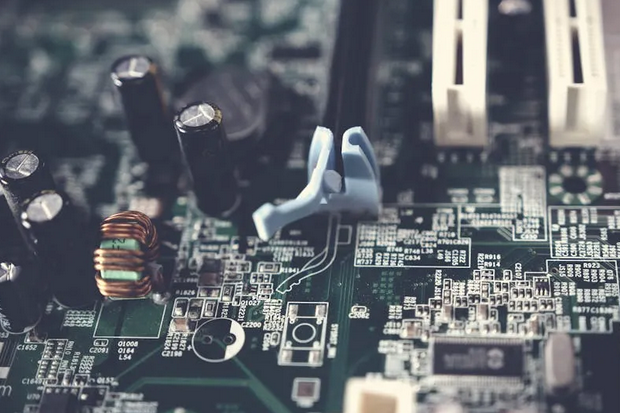

在PCB设计中,由于电子工程师的评估错误,很容易留下死铜(孤岛)问题,那么有必要去掉这个死铜?很多新人工程师都不知道如何解决,今天凡小亿将根据这个问题展开讨论,希望对小伙伴们有所帮助。1、死铜是什么?有什么危害?死铜指的是在PCB设计中未被

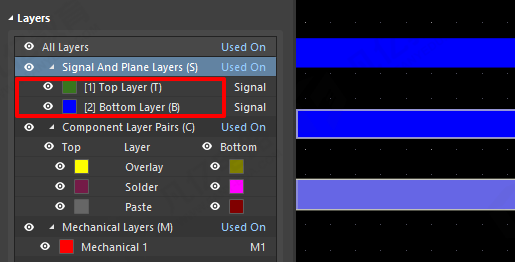

大GND铜皮没有网络,导致多处孤岛铜皮靠近管脚放置,走线或铺铜直接连接到引脚不要接到电源层rx、tx分别建立等长组控100mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

现在网络上大量的EDA软件视频教程,帮助学生和初级电子工程师更快的熟悉软件使用方法,入门是真的快啊。原理图设计的时候,如果你对元器件特性不明白,不知道电源怎么设计,带负载能力不清楚,单板电流消耗,单板处于休眠或者正常工作状态等等不清楚,那可以肯定是一个失败的设计!但是对于PCB设计来说,初学者很快就

1.外壳地和gnd连接处,外壳地这边需要和gnd打一样多的孔2.器件摆放太过密集,注意丝印不要重叠,保持一定距离3.存在尖岬铜皮和孤岛铜皮,可以挖空或者在末端打孔4.走线保持3w间距,绕线拐角处角度大点避免直角以上评审报告来源于凡亿教育90

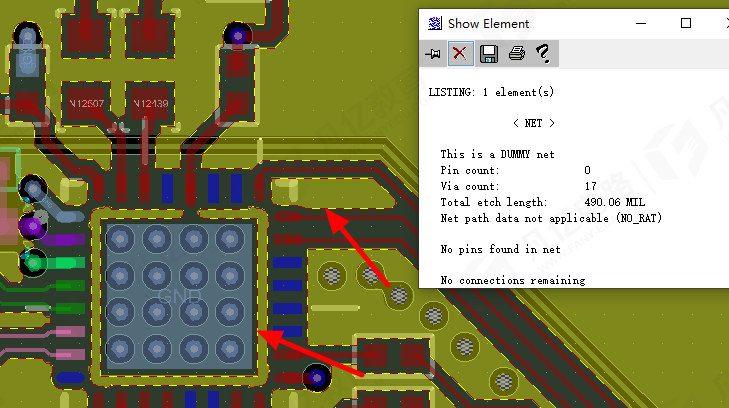

1.过孔应打到最后一个器件的后方,反馈信号需要连到最后一个电容。2.多处过孔上焊盘3.电源信号连接处铜皮需要加宽载流4.多处孤岛铜皮和尖岬铜皮5.注意保持过孔之间间距和过孔到焊盘间距不能太近6.电源信号走线需要加粗保持前后线宽一致7.走线不

铜皮间距太小,所有间距最小不能小于4mil多处孤岛铜皮、尖细铜皮差分出焊盘尽快耦合优化布局走线尽量靠近,不会可以查看参考板走线太细,走线一般情况最细4mil,明明可以走4mil线宽差分对内等长绕线在引起不等长处绕线差分对内等长绕线拱起处长度

在PCB设计中,死铜即孤岛铜算是常见的问题,是指那些没有电气连接,孤立存在电路板上的铜区域,然而很多电子工程师遇见死铜,都在忧虑是否要去除,下面本文将从多角度来分析,希望对小伙伴们有所帮助。1、死铜能带来什么问题?①EMI问题:死铜在电路板

扫码关注

扫码关注