- 全部

- 默认排序

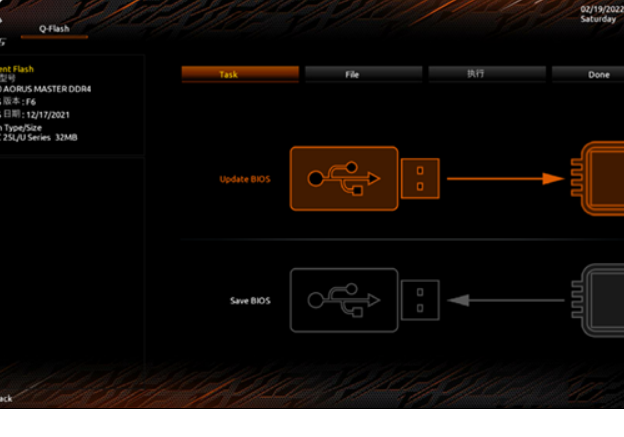

很多人电脑开机时第一个见到的就是BIOS界面,文本模式的传统BIOS由于太过落伍,已经被AMD、Intel及微软、苹果等厂商放弃了,转向了UEFI BIOS,现在Win11都是强制需要UEFI BIOS才行的。还有一些操作系统出于各种原因没

一般缺乏经验的工程师或者学生,拿着一个项目任务书,或者一个成品的电路板的时候,往往会感觉到,根本无从下手。主要原因是,知识储备不足,少实践少动手。但也不用着急,这是需要慢慢积累的。同样,不用担心东西太多,不知道学到什么时候才能独当一面,因为

AD21!在画原理图时感觉A4图纸太小了,然后右击->原理图优先项===修改图纸大小(如设A3)。但是图纸是没有增大的,是什么原因?过去的protel,DXP,旧的AD09都没有此问题,当前电脑系统是W10;谁能解决

在电子工程领域内,串行接口和并行接口都是常见的数据传输方式,然而串行接口在特定情况下却会比并行接口更快速和高效,很多工程师都不明原因,下面这篇文或许能给你些思考。1、串行接口传输方式的特点一般来说,串行传输是逐位地将数据一位接一位地传输,通

在公差分析中,如果尝试使用公差脚本载入某个已保存的评价函数时,如果在 Tolerancing 中点击 Check 按钮,对应返回的值将与在 MFE 中直接返回的总 MF 值不相同,请问这是什么原因造成的?如下图所示:[color=var(-

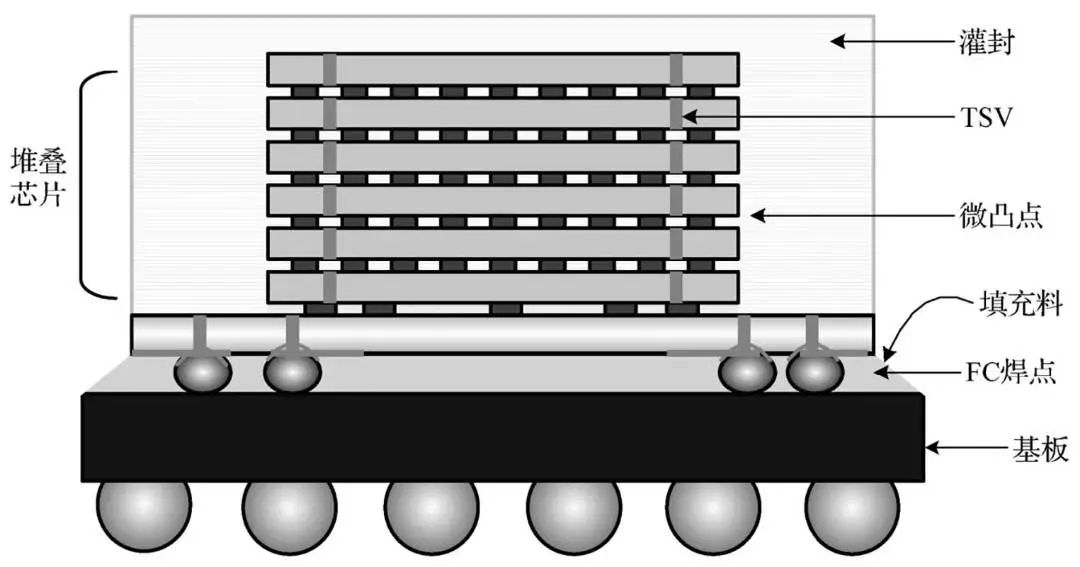

SiP失效模式和失效机理

SiP组件的失效模式主要表现为硅通孔(TSV)失效、裸芯片叠层封装失效、堆叠封装(PoP)结构失效、芯片倒装焊失效等,这些SiP的高密度封装结构失效是导致SiP产品性能失效的重要原因。一、TSV失效模式和机理TSV是SiP组件中一种系统级架构的新的高密度内部互连方式,采用TSV通孔互连的堆叠芯片封装

系统级信号完整性(SI)仿真是高速PCB设计的重要概念,其存在间接联系着高速PCB电路设计的正常运行,但有很多小白不清楚,甚至错将系统级SI仿真和普通的SI混为一谈,这是错误的思维误区,我们要尽量避免。一般来说,现在的EDA信号完整性根据主

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。接下来我们就来讲讲常见的DRC设置有哪一些。

前些天硬盘坏了,幸好不是系统盘,不然那些软件安装配置会把我折腾坏,或许这也是在暗示我该换电脑了。重要的数据部分没有遭到损坏,数据是无价的,还是要勤备份。于是换上了一张新的硬盘:当时脑袋里面就闪过一个问题,为啥 windows 系统不从 A 盘开始分区显示了?其实原因也比较简单,在计算机发展历史的长河

扫码关注

扫码关注