- 全部

- 默认排序

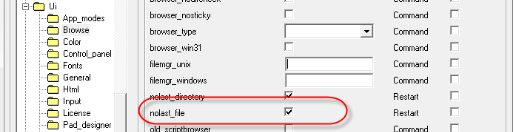

答:我们使用Allegro软件设计PCB,当关闭Allego软件,重新打开Allego软件,打开的是上次操作过的PCB文件,这是系统的默认设置。我们这里讲解一下,如何进行设置,打开Allegro软件时显示的是一个空的PCB文件,具体操作如下所示:

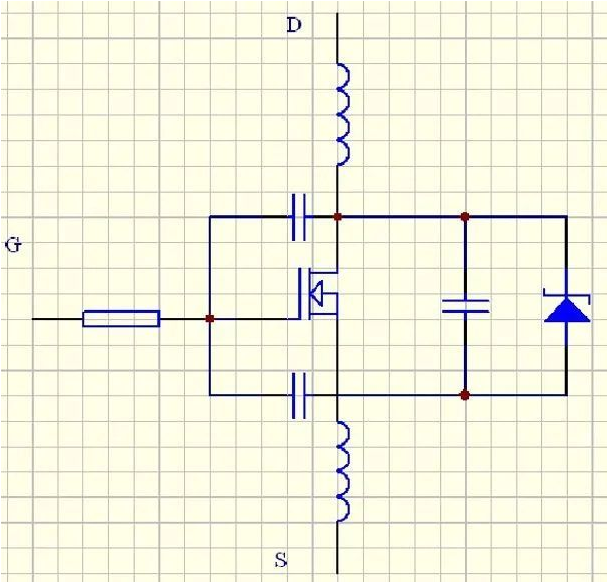

关于MOS管驱动电路设计,本文谈一谈如何让MOS管快速开启和关闭。一般认为MOSFET(MOS管)是电压驱动的,不需要驱动电流。然而,在MOS管的G极和S极之间有结电容存在,这个电容会让驱动MOS变的不那么简单。下图的3个电容为MOS管的结

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

创建好原理图原器件以后,在SCH Library 界面点击选择创建好的原件,接着点击下面的编辑。如图1所示。弹出原器件属性编辑框,如图2所示。点击Comment后面的小眼睛图形既可关闭显示Value值。图1

我们在使用Allegro软件的时候,除了在上面一栏有很几排的工具栏菜单以外,上面是显示常用的一些命令还有工具,还有一些窗口显示,比如Find面板窗口、Visiblity面板窗口、Options面板窗口等,如图5-38所示。

1、什么是busoff?BUSOFF,从字面意思可以看出,表示总线的关闭,此时ECU从总线脱离,既不能接收总线的报文,也不能向总线发送报文。 2、BUSOFF是如何产生的?CAN总线上存在多种错误状态,包括:位错误(Bit Check Error)、位填充错误(Bit Stuff Error)、C

扫码关注

扫码关注