- 全部

- 默认排序

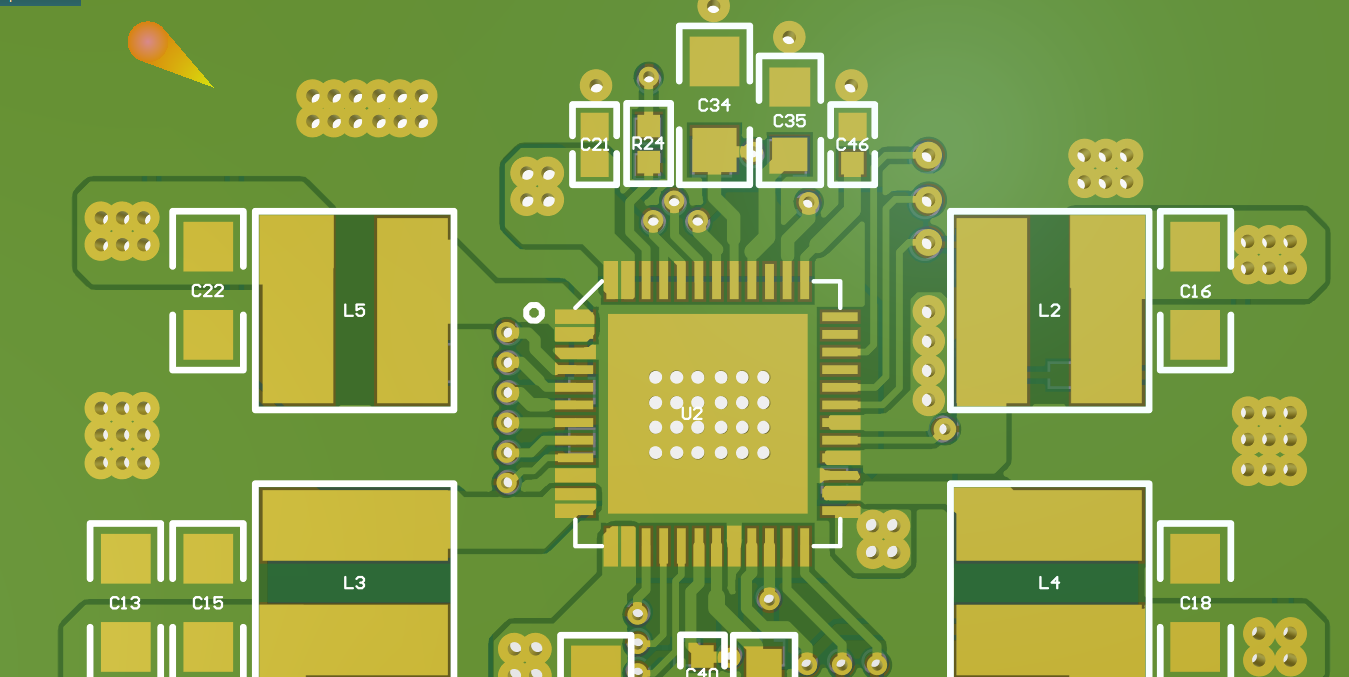

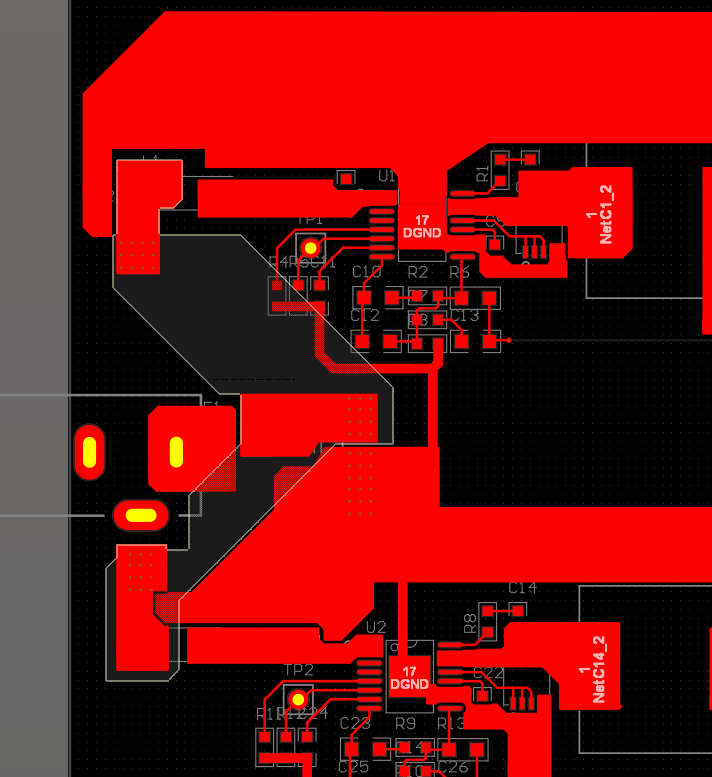

整板过孔除了IC散热焊盘其他的都盖油处理:电感底部不要放置器件以及走线:电阻电容可以塞到IC的底部进行布局,自己调整下。注意板上的铜皮不要出现这种直角,尽量都钝角铺铜,其他如果存在类似情况自己都修改下:焊盘内走线的宽度最多与焊盘同宽,拉出焊

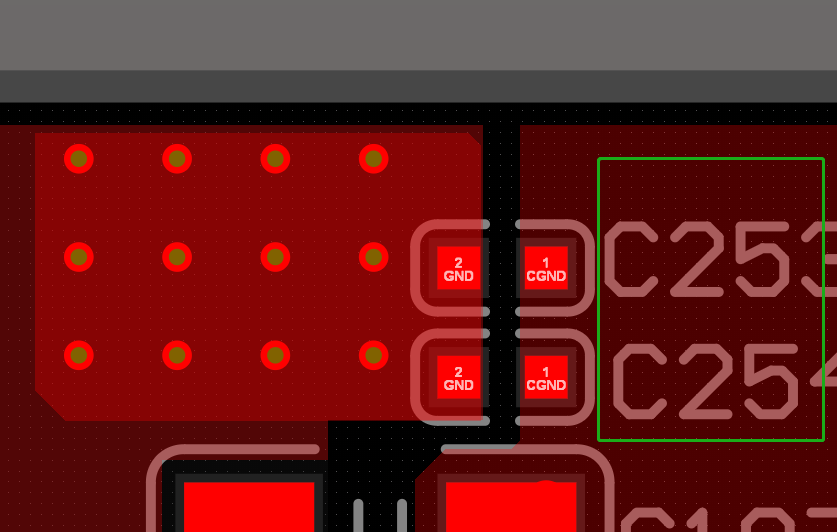

跨接器件两边多打点回流地过孔进行回流:电源地跟机壳地之间至少满足2MM间距:从焊盘拉差分走线需要保持耦合,优化下:差分间距都不一样了,没保持耦合,注意修改,重新走差分线:不要出现直角:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

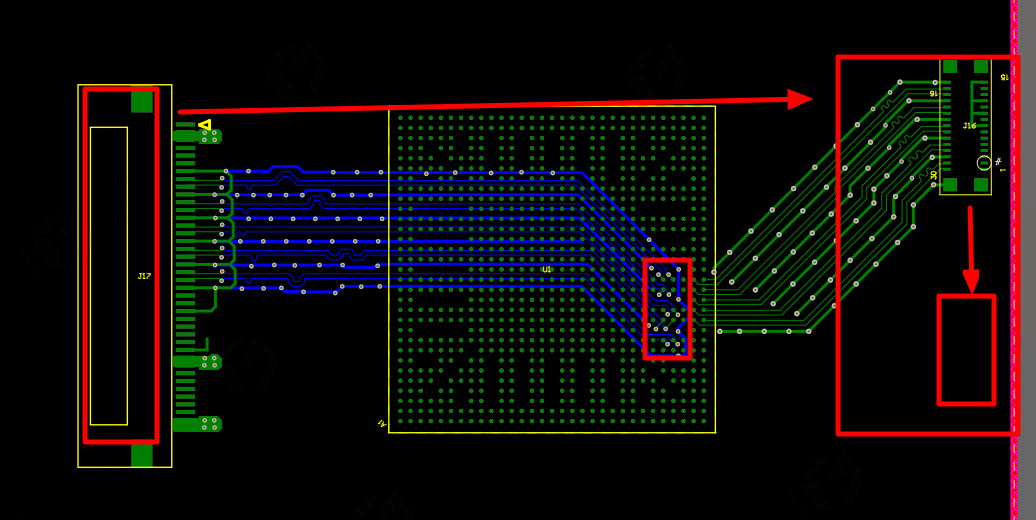

器件布局应该在BGA上对应焊盘的方向,尽量缩短走线,2.差分对内等长Space的高度是1倍到2倍间距的高度。3.差分包地应该尽量包过来4.走线在焊盘中应该和焊盘保存等宽5.包地线很长一段走线没有打孔。以上评审报告来源于凡亿教育90天高速PC

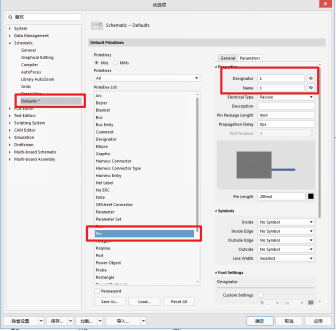

在绘制原理图的时候,有时出现失误。绘制的原理图封装出现问题,去库中修改了,可以不用在原理图中把原先的放置好的删除掉。可以在库中把修改好的器件直接更新进去既可,这样可以省去很多的设计时间。第一步:首先打开原理图库文件,找到需要修改更新的原器件

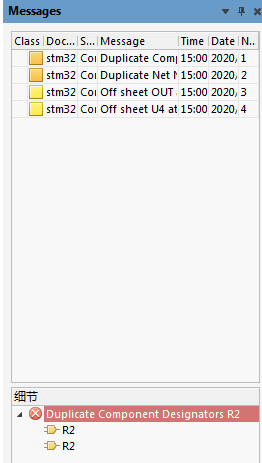

我们在编译完原理图之后有时会看见红色的波浪线,这些红色的波浪线时我们在编译后的错误显示,提示这个地方有错误。这时候我们只需要在“Messages”里面查看对应的错误类型并修改即可。

这样的做法在早期做小型电路时还可以应付,随着电路设计的规模越来 越大。复杂度越来越高,这种设计的方法也不能再适应现代化设计的需要。不仅仅如此, 在电路板图设计时也是一个相当复杂的过程。在进行手工设计电路板图时,需要进行元件 布局,绘制草图,修改草图,才能绘制出所需要的电路图。随着电子元件的增多,电路板 的尺寸的减小,电路的层数也越来越多,布线就成了相当的难度。导致已经无法再进行用 手工设计了,另外随着元件数量的增多,各元件之间的相互干扰,各元件之间的干扰,耦 合也

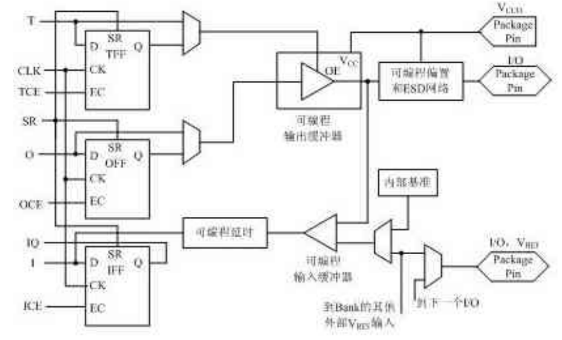

FPGA是当今数字系统设计的主要硬件平台,优点是完全由用户通过软件进行配置和编程,可以反复擦写,无需改变PCB电路板即可修改升级,极大地缩短了系统设计的周期,提高了实现的灵活性降低成本,因此极大地获得了硬件工程师的青睐。所以本文将重点分享F

答:这个功能对于很多初学者都不是很清楚,有些同学可能因为之前随意放置过几个PIN管脚,导致后来放置管脚的时候,管脚编号不是从1开始的,这样就会造成很多的疑问。 1)双击管脚,进入属性里面修改管脚编号可以完成编号的更改。但此种方法,治标不治本,下次再放置管教时,还是不会从修改以后的管脚编号开始。

铜皮全部是直角,尽量全部都修改为钝角的:主干道器件摆放需要整体中心对齐:电感当前层内部需要挖空:焊盘出线需要从两长边拉出:电源输入输出对应的地在中间的IC焊盘上打孔过孔,进行单点接地:地直接优化下铺铜连接进来:其他的没什么问题了。以上评审报

在设计原理图库原件的时候,原件过小。但是器件管脚长度过长,显得器件很不协调。第一步:执行快捷键命令PP放置管脚,如图1所示。图1第二步:双击管脚,弹出属性框,在PIN length处修改既可。如图2所示。图2

扫码关注

扫码关注