- 全部

- 默认排序

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

今天遇到了这个问题,领导让我改成135°线,说这样不行电路板好看很重要吗,没谁天天盯着电路板瞅吧他给我的回复不是好不好看是他觉得有问题刚我搜的因为我认为直接走线会比45更好因为我要辞职了,然后我回复他我说我记得之前培训(或者还是那个技术文章)任意走线会比45好一些,弯越多信号反射越大,所以我现在布线

一堆分立元件如何布局

请问,电路图主要就是一些分立元件,是按照这些元件的相互之间的就近原则布局,还是把相同类型的元件摆放在一起然后布局。 如果按照元件的相互间信号流动的就近原则的话,布局看上去特别乱,如果把相同类型的元件放在一起,然后布局,担心影响后面的信号走线。 不知道怎么弄。

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

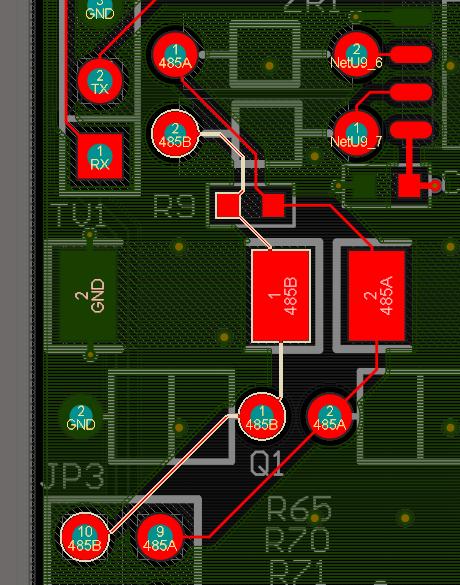

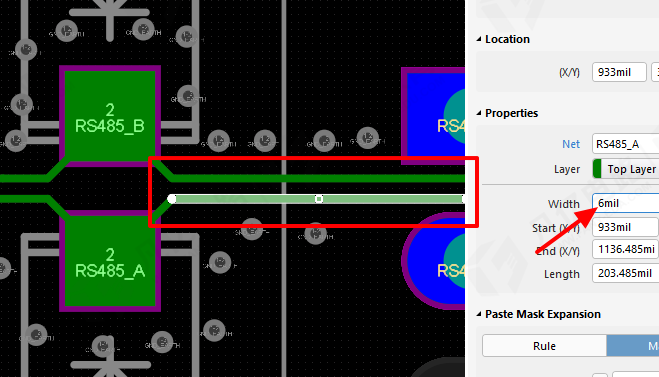

1.485走类差分需要优化一下2.模拟信号走线需要加粗处理3.晶振走线需要优化一下,尽量走类差分处理4.差分对内等长误差5mil5.跨接器件旁边要多打地过孔,分割间距建议1.5mm,有器件的地方可以不满足6.模拟信号呈一字型布局,走线加粗7

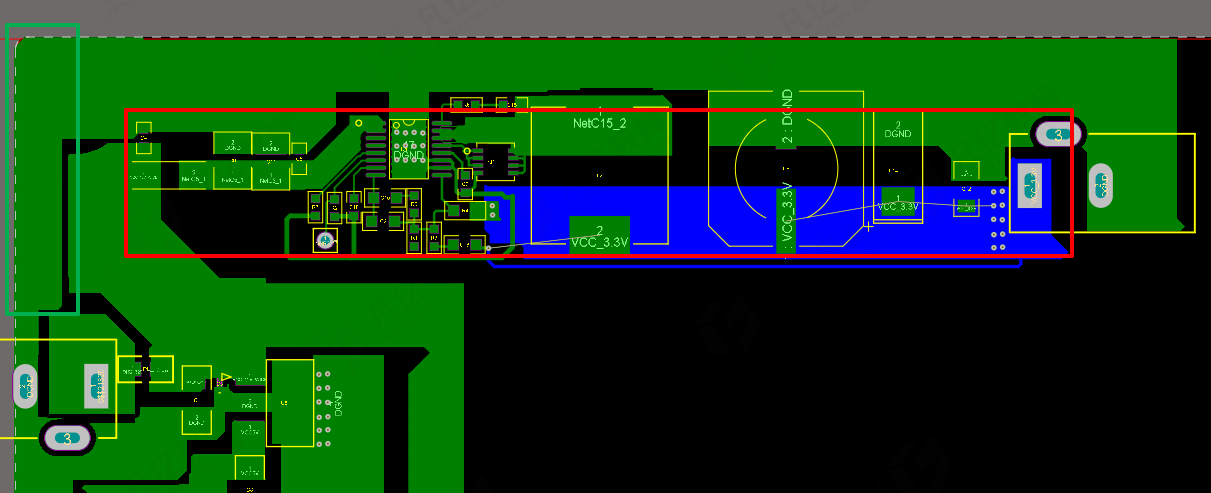

红圈内的是一整路dcdc电路,只需要这些器件地焊盘连接到一起在芯片下方打孔,不需要把整个电路板的地焊盘都一起连接焊盘避免从长边、四角出线反馈信号走线连接到dcdc电路最末端顶层焊盘没有连接铺铜走线尽量避免直角锐角器件摆放太近相互干涉电源主输

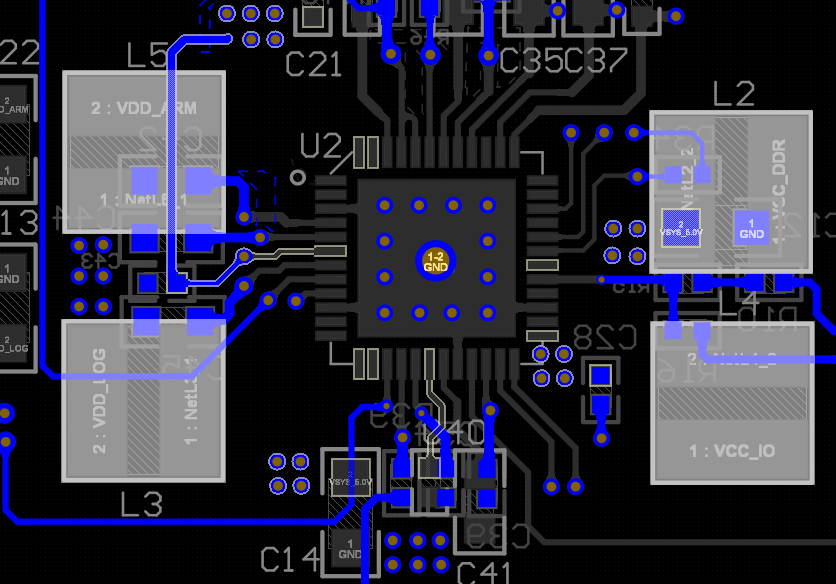

电感底部不要放置器件,优化下布局:电感内部的铜皮需要挖掉:信号走线不能从电阻电容内部穿过,优化下走线路径:整体需要特别处理的就是电感底部的电容,不能放在电感底部,需要优化布局。其他的DCDC以及LDO没什么问题。以上评审报告来源于凡亿教育9

485信号线应按加粗类差分处理,走线最少加粗到8mil以上232的C+C- V+V-所接电容属于升压电容,走线按电源走线加粗tx、rx信号走线用gnd打孔隔开以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程

扫码关注

扫码关注