- 全部

- 默认排序

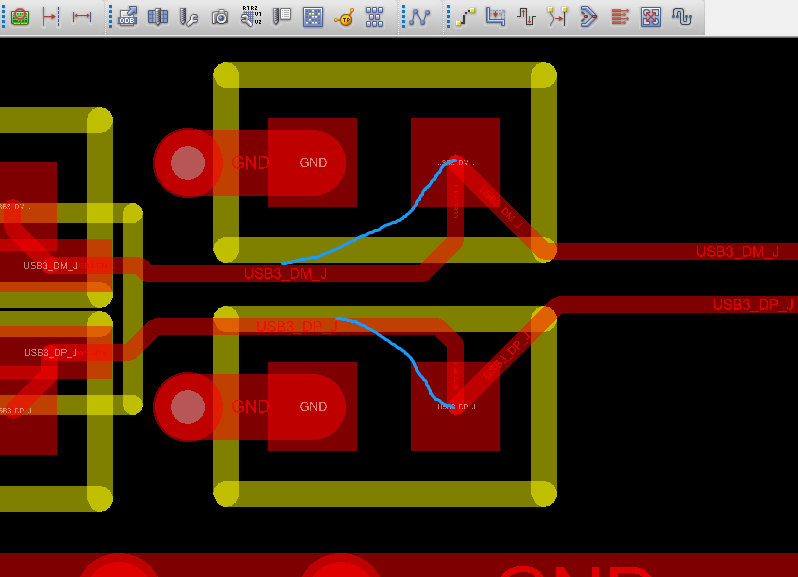

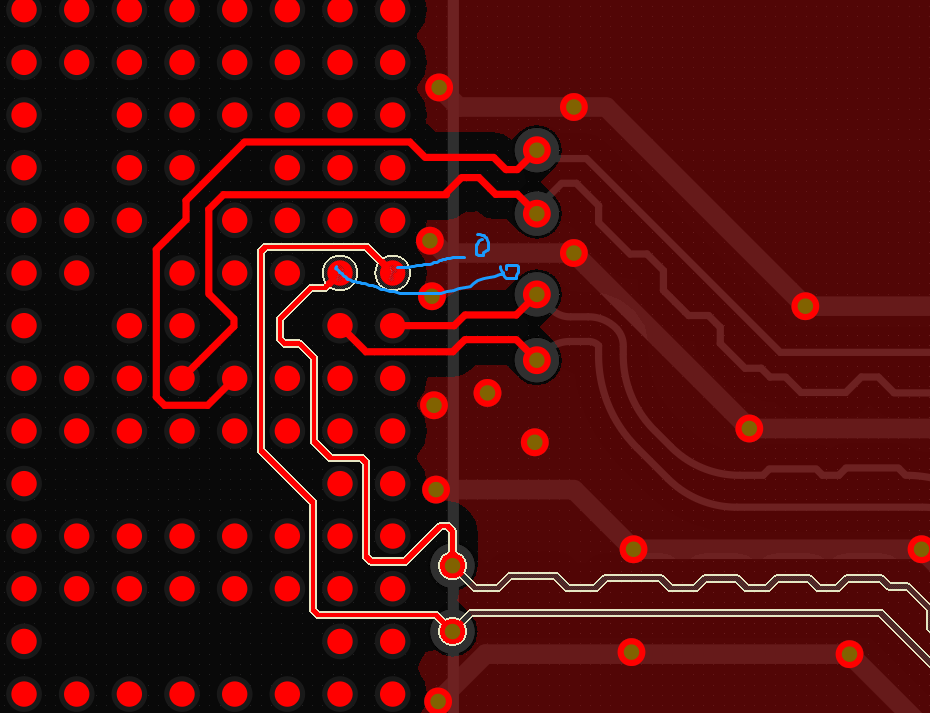

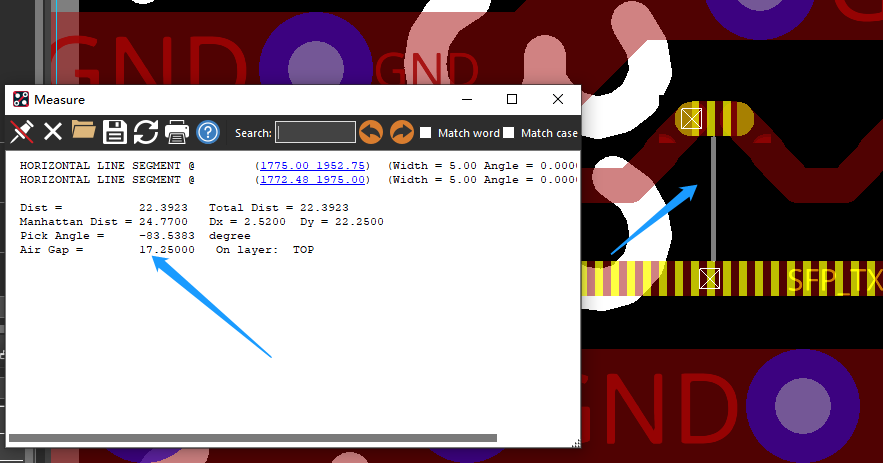

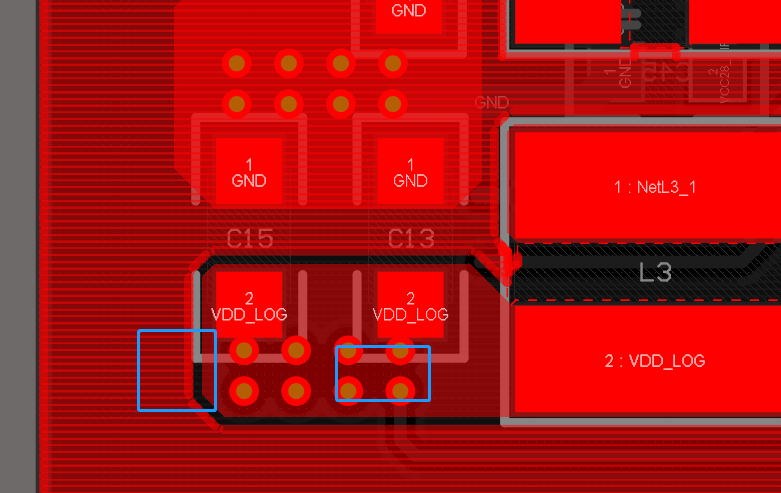

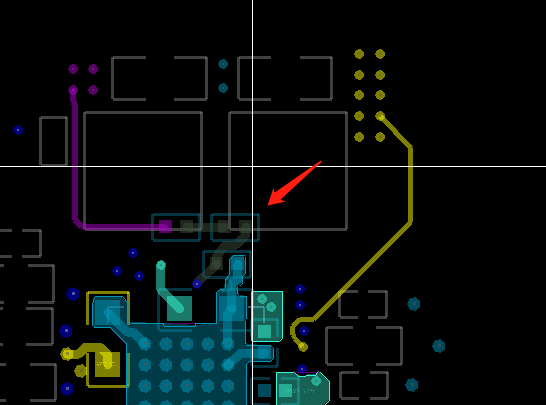

差分出线可以在尽显一下优化2.差分走线要尽量耦合3.差分走线不满足差分间距要求4.锯齿状等长不能超过线距的两倍5.存在开路后期自己在地平面层铺一下整版铜,把地尽量连接6.线宽尽量保持一致7.USB差分对内等长误差5mil以上评审报告来源于凡

差分走线不满足差分规则,出线不耦合2.此处直接扇孔去底层连接3.差分线修理不当4.此处一个地不用进行处理,直接铺铜即可此处走线需要优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

Protel DXP是第一个将所有设计工具集于一身的板级设计系统,电子设计者从最初的项目模块规划到最终形成生产数据都可以按照自己的设计方式实现。Protel DXP运行在优化的设计浏览器平台上,并且具备当今所有先进的电路设计软件特点,能够处理各种复杂的PCB板设计过程。通过设计输入仿真、PCB板绘制编辑、拓扑自动布线、信号完整性分析和设计输出等技术融合,Protel DXP提供了全面的设计解决方案。 PCB板电路设计的原则包括以下几个方面:

差分对内等长凸起高度不能超过线距的两倍差分走线不满足差分阻抗间距要求3.光口模块座子下面需要所有层挖空处理4.后期自己在电源层铺铜尽量连接差分出线方式需要再优化一下跨接地旁边可以尽量多打地过孔以上评审报告来源于凡亿教育90天高速PCB特训班

前面我们讲到PCB的拼版是一个至关重要的环节,它不仅影响着产品的生产效率,也直接关系到产品的质量和成本。合理的拼版能够优化生产流程,减少浪费,提高产能。然而,在实际操作中,由于各种因素的影响,很多工程师的PCB拼版存在着不少问题。本文将带您

输出打孔要打在最后一个电容后面2.反馈取样要从最后一个电容后面取样,线宽需要走10mil3.注意电感底部不要放置器件以及走线,需要重新优化下底层的布局以及布线:4.过孔尺寸尽量用常规的,8/10,8/16,12/24,一般pcb上过孔大小尽

电感下面不要放置器件,自己优化下:此处DCDC5.0V输入建议铺铜处理以满足载流大小,或者加粗走线的宽度能满足:此处存在铜皮瓶颈处,自己优化下:此处LDO电路中的电源信号能顶层连接的,就把过孔删掉:存在多处情况。右边的LDO电源信号存在上述

器件放置安装孔不要超出板框2.差分走线不满足差分间距规则3.铜皮避让存在开路4.此处走线可以在优化一下,走线路劲尽量短5.差分出现要尽量耦合6.差分对内等长误差5mil7.等长Gap要尽量大于3W以上评审报告来源于凡亿教育90天高速PCB特

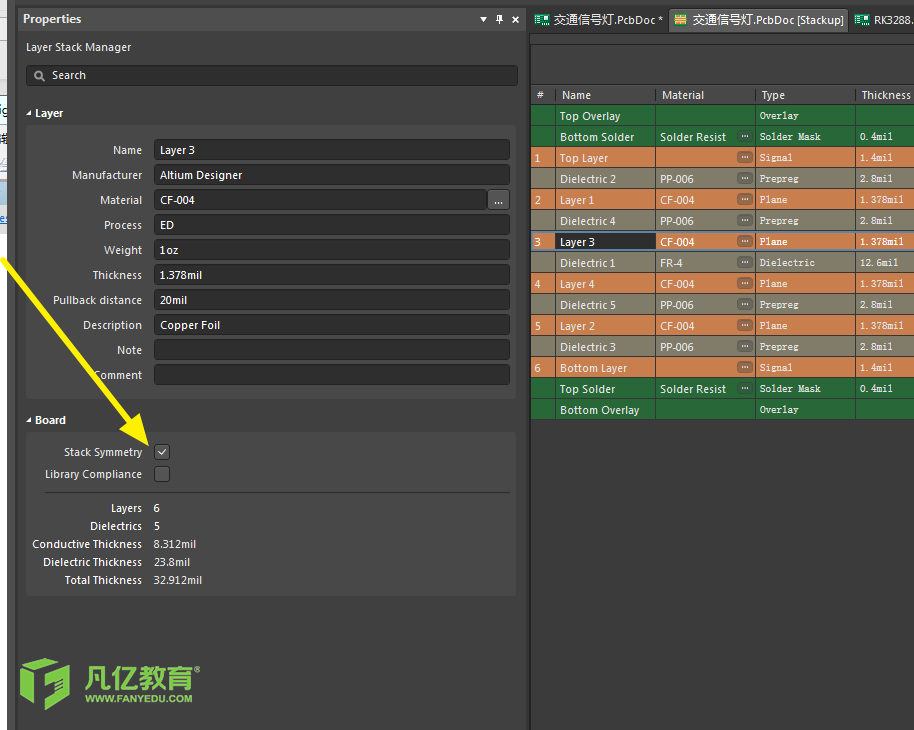

对于AD爱好者来说,每一次的版本更新都是新功能的添加和旧功能的优化或者是移除,在新版AD19在内电层内缩pullback进行了位置变化,同时内电层改变内缩还相邻的内缩会一起变动。

Avant-G——专为通用中端应用优化说明Avant-G系列中端通用FPGA基于Avant平台构建,为通信、计算、工业和汽车市场的中端应用提供低功耗、先进的互连和优化的计算能力。Avant-G器件提供领先的信号处理和AI、灵活的I/O,支持

扫码关注

扫码关注