- 全部

- 默认排序

在现代高速电子设备中,PCB板的阻抗测量和控制是至关重要的技术,准确的阻抗设计和测量可确保产品的信号完整性、抑制信号串扰及提高系统性能,因此是很多电子工程师的重点学习内容,下面聊聊PCB阻抗测量及控制方法。一、PCB板上如何测量阻抗?1、T

包地与串扰

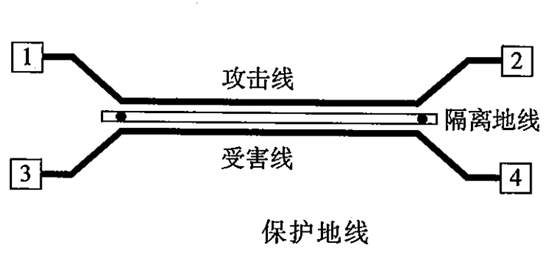

工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GN

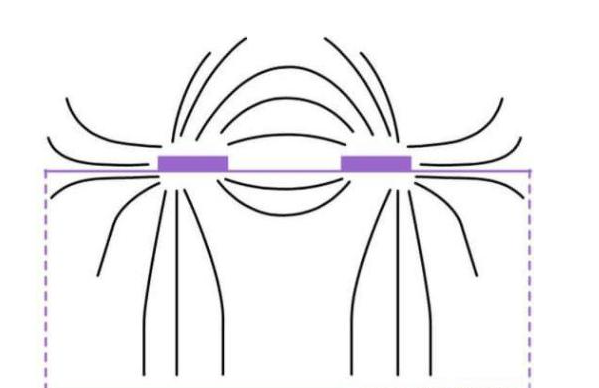

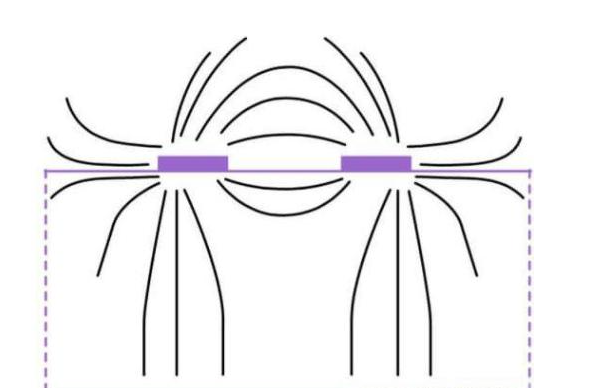

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

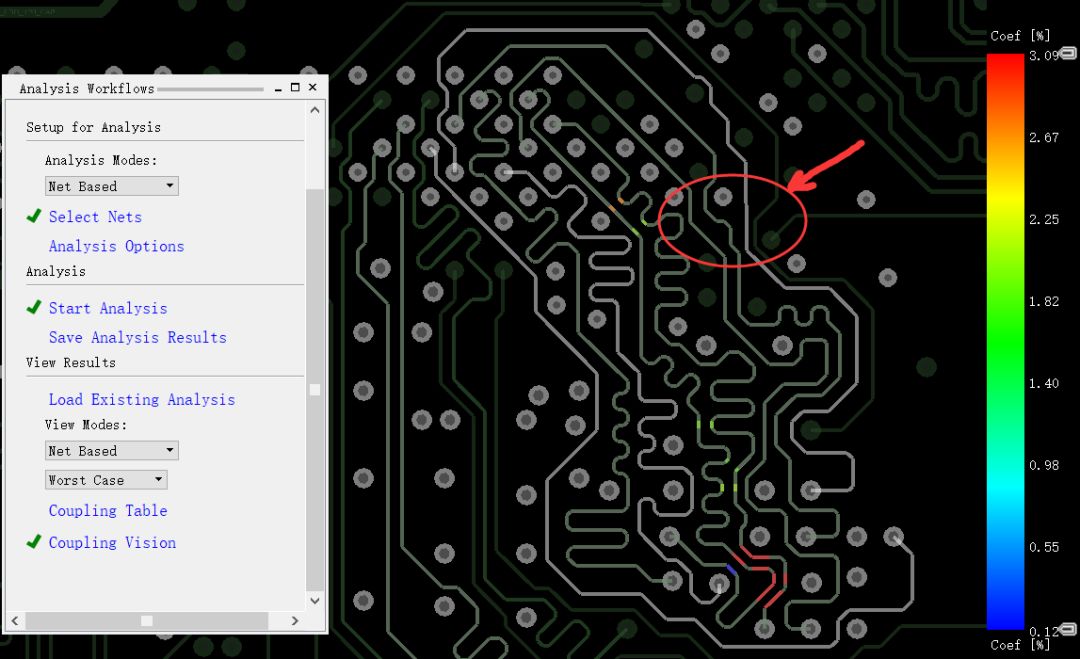

一个layout工程师学习信号完整性之路串扰还是比较复杂的一个东西,在工作中好多人询问串扰仿真怎么分析,其实对于仿真流程相对简单,但是真正利用这个仿真去做优化的相对较少,所以还是要理解其中的原理,在layout中去设计,比如常说的3W等,也

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

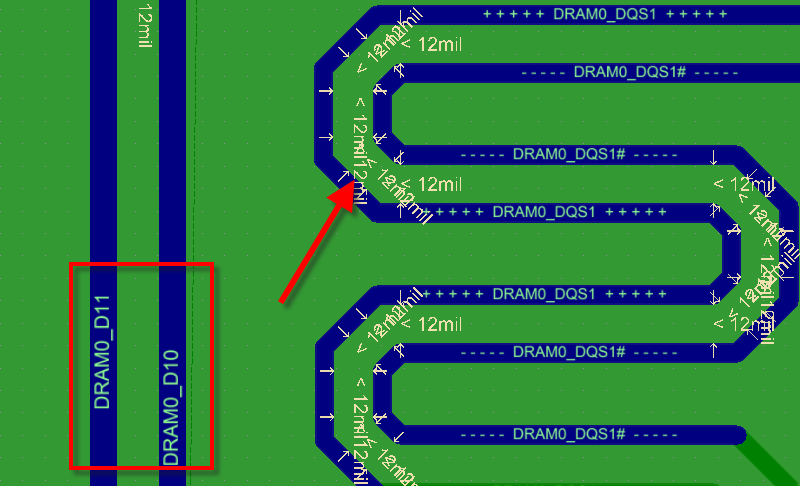

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

全站最新内容推荐

- 1AD-全能20期-SMT32-两层板-20期-杨文越

- 290天全能特训班22期-莱布尼兹的手稿 第十九次作业 SDRAM

- 3飞龙套餐allegro篇(PCB、硬件、EMC、单片机)

- 4飞龙套餐Altium Designer篇(PCB、硬件、EMC、单片机)

- 5飞龙套餐PADS篇(PCB、硬件、EMC、单片机)

- 6AD-全能21期-DM642开发板第一次作业

- 72024年中国及31省市3D打印市场分析及国家政策汇总

- 8AD- 杨皓文 第七次作业 2片SDRAM设计(菊花链)

- 990天全能特训班22期AD-沸点-2SDRAM

- 102.4GHz/6GHz Wi-Fi 带通滤波器: ACPF-7A24-TR1、ACPF-W065-TR1 产品介绍、特征及应用

扫码关注

扫码关注