- 全部

- 默认排序

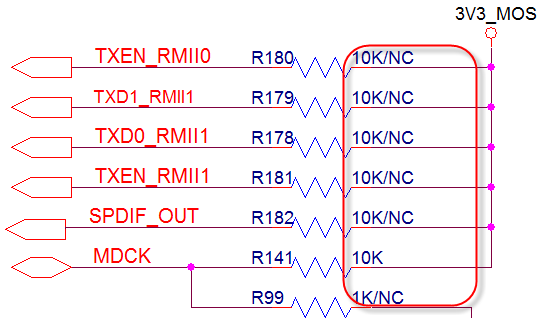

针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称name以及管脚编号Numbers先按数字1、2、3...,一

Orcad输出网表出现“Duplicate Pin name”的错误,应该怎么处理呢?

答:在绘制原理图时,放置出来的元器件,在图纸上都是显示器件的参数的,就是Vaule值,如图2-53所示,对于单个的属性参数,我们双击那个参数,会弹出Display Properties的对话框,如图2-54所示,在下面的对话框选择是否需要显示参数即可,Do Not Display表示都不显示;Value Only表示只显示Value值,也就是封装名称;name and Value表示都显示。 图2-53 显示参数值原理图部分示意图 图2-54 显示参数设置

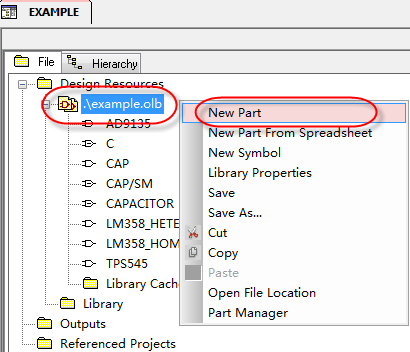

答:第一步,执行菜单命令File→New→Library,新建一个原理图库文件,如图2-1所示: 图2-1 新建原理图库示意图第二步,会弹出新建好的olb文件,然后选中新建好的olb文件,单击鼠标左键执行New Part功能,新建一个单个的器件,如图2-2所示,第三步,在弹出的New Part Properties属性框中,输入相对的参数,如原理库的名字(name)、原理图库编号的起始字母(Part Reference Prefix)、PCB封装名称(PCB &

在学习电路设计软件过程中,总会遇到诸多电路设计软件相关难题。为帮助大家解决常见的电路设计软件问题,小编特地带来本文。请注意,本文有关电路设计软件的问题讲解基于protel。如果你想在电路设计软件的学习道路上再进一步,不妨来了解下这些问题哦。 1.原理图常见错误: (1)ERC报告管脚没有接入信号:a.创建封装时给管脚定义了I/O属性;b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;c.创建元件时pin方向反向,必须非pin name端连线。 (2)元件跑到图纸界外:没有在

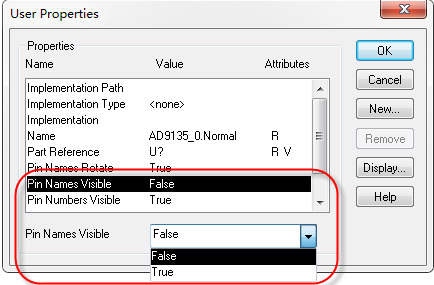

答:在设计原理图库的时候,除了IC类器件需要显示网络的名称以外呢,一般其它的原理图库是不需要显示网络名称的,主要是显示器件内部的连接关系,所以我们需要隐藏掉原理图库中的网络名称,操作步骤如下:第一步,打开所要隐藏网络名称的库文件,点击菜单Options→Part Properties编辑属性;第二步,在弹出的属性框中选中Pin names Visble,修改Value值属性即可;第三步,需要显示网络名称的,Value值那一栏选择True;隐藏网络名称的,Value值那一栏选择False,如图2-

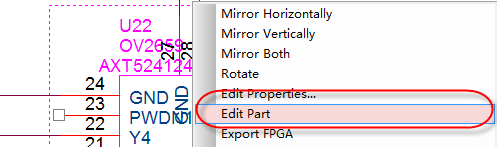

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36041): Duplicate Pin name "GND" found on Package LCM0200CE1A0_3 , U22 Pin Number 25: SCHEMATIC1, 23.Camera (129.54, 50.80). Please renumber one of these.解决的办法如下所示:第一步,找到报错的器件U22,然后选中U22这个器件,点击右键,选择Edi

DRC问题

报错内容如下:Polygon named: Bottom Layer-No Net In net GND On 01Top Layer但是AD9却不会报此类错误,请教各位大佬这是怎么回事。

Cadence 17.4 画好 Symbol 后,Pin name 总是挤在一起(已经调整N遍,更新库文件了)这个有解吗

扫码关注

扫码关注