- 全部

- 默认排序

操作方法如下所示:第一步,按照前面所述的方法,新建一个库文件,绘制好外形框;第二步,点击右侧边栏Place Pin Array,按一定排列顺序来放置管脚,如图2-66所示, 图2-66放置序列管脚示意图第三步,弹出的Place Pin Array属性框编辑需要放置管脚的个数数目以及属性即可,参数设置含义如下所示:l Starting name:起始管脚的名称,这个先设置数字,后面编属性统一更改;l Star

17.4制作pad命名时提示“Maximum padstack name is 15 characters”,最大padstack名称为15个字符,可以忽略吗?

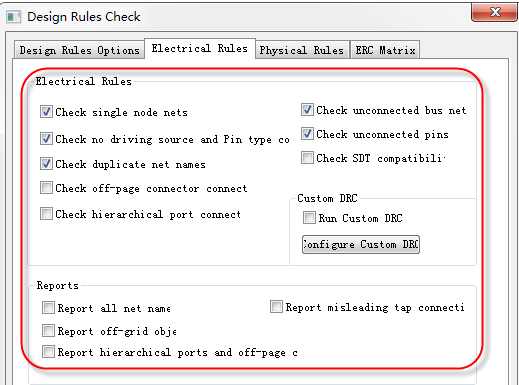

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:第一步,首先在绘制库的界面中按照规格书放置IC相对应的管脚数目管脚名称name以及管脚编号Numbers先按数字1、2、3...,一

Cadence 17.4 画好 Symbol 后,Pin name 总是挤在一起(已经调整N遍,更新库文件了)这个有解吗

DetailsNets Wire BOOT1 has multiple names (Net Label BOOT1,Net Label BOOT1,Net Label PB2,Net Label PB2)

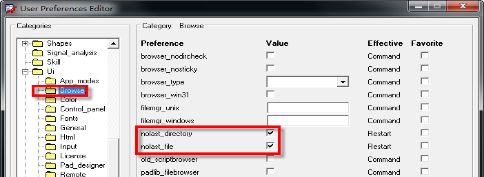

答:使用Allegro软件设PCB,打开Allegro软件,一般显示的文件为上一次操作过的.brd文件,这是Allegro软件安装的默认设置。在实际的项目中,需要Allegro打开后,显示的是一个空文件unnamed.brd,可按以下步骤操作。

在Logic软件中使用Bus总线的时候,有以下几个注意事项:第一,总线不是强制使用的,不使用总线也是可以的,使用总线构架是使得原理图更加清晰,分析原理图更加透彻,第二,总线命名方式一定要按照如 Busname[00:24]这种方式,然后信号分支网络标号的命名方式与总线保持一致。

按照破解步骤进行,到License Server Data 这一步出问题,Host name更改没问题,但是Log File 没有找到debug.log,接下来提示:StartService failed:UNKNOWN(找不到服务器)请问各位大神怎么解决这个问题,debug.log这个文件路径哪里

扫码关注

扫码关注