- 全部

- 默认排序

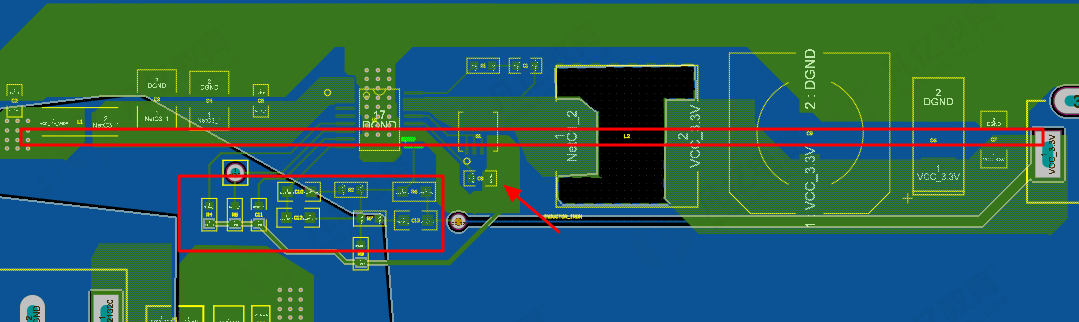

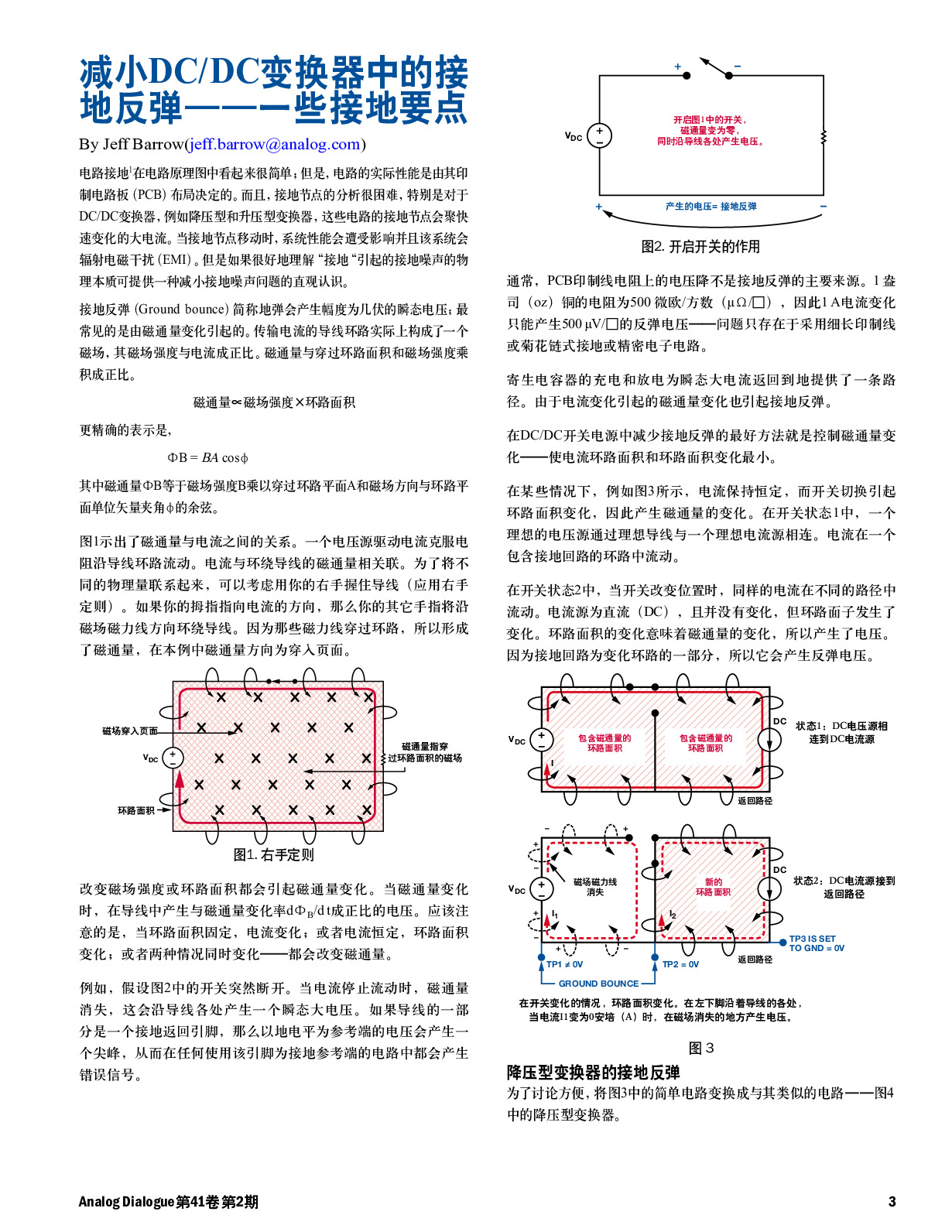

如下图为典型的dcdc电路:芯片是台湾省立琦科技的。上图为dcdc典型应用电路,CIN为输入滤波电容,CBOOT是上管驱动“自举”电容,L是储能电感,R1和R2是反馈电阻,CFF是前馈电容,COUT是输出滤波电容,RT是内部运放补偿器件。一

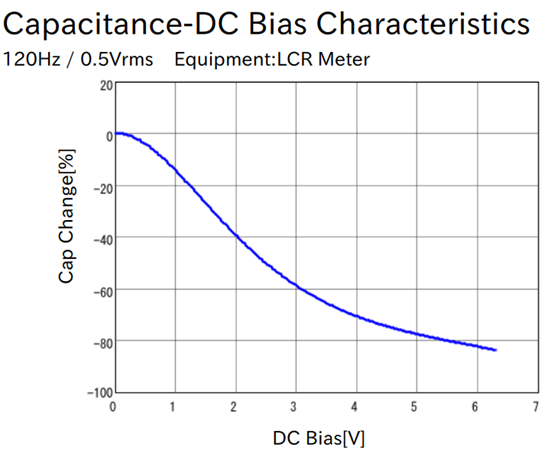

dcdc实测出来的纹波比公式计算出来的大,电容ESR的锅?我们设计dcdc电路的时候,经常会用下面的公式计算一下纹波输出电压,然后在输出端选择合适的电容。下面是某dcdc规格书的纹波说明: 陶瓷电容的ESR都说很小,可以忽略。那么根据输入输出电压,开关

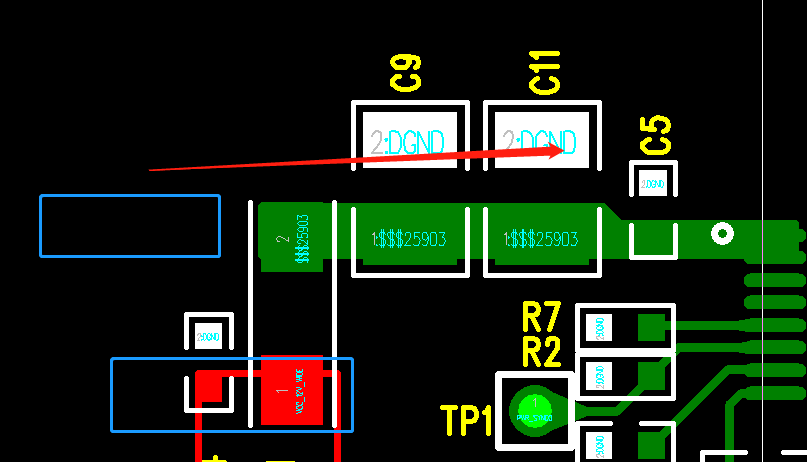

器件尽量中心对齐,相邻器件尽量朝一个方向放置不要任意角度铺铜,铜皮任意角度的斜边全是毛刺铺铜尽量避免直角锐角要求单点接地电容离芯片管脚太远,器件应靠近对应管脚放置,连接线尽量缩短焊盘要从短边出线,避免从焊盘长边出线和四角出线以上评审报告来源

电感下面要挖空处理过孔打规范,不要紧挨焊盘会造成焊锡流入过孔导致虚焊,过孔重叠了。丝印需要调整一下太乱了太大太细了。电感垂直摆放以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:ht

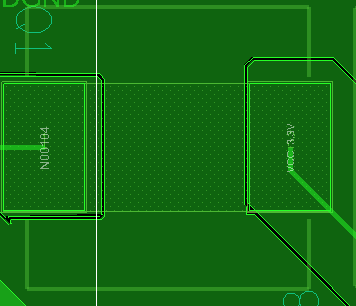

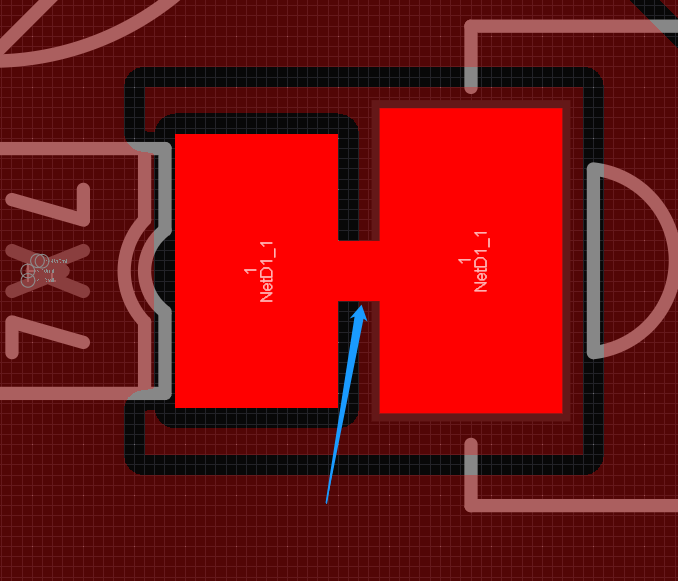

主干道尽量呈一字型布局2.dcdc采用单点接地,输入输出的地需要连接在芯片的扇热焊盘上3.采用单点接地此处不能打孔,可直接铺铜进行连接4.器件摆放尽量中心对齐5.PCB上还存在DRC以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如

LDO应用要点

(1) VRF滤波由LDO的工作原理可知,Vref(基准电压)的稳定性与LDO输出电源的纹波及噪声密切相关。为了减小器件面积,某些LDO在片内不提供对VREF引脚的滤波。在这种情下,设计者需在VREF引脚附近添加10uF电容,以保证VREF的低噪声和低纹波(2) SENSE(感应)引脚的处理SENSE引脚是LDO、dcdc电源芯片上常见的引脚在PCB上,当电源输出端与负载端相距较远时,输出电源Vout需通过较长距离的PCB导线(或PCB铜皮)才能加载到负载上,由于负载电流流经

电源输出主干道采用十字连接注意要满足载流可以后期自己添加一块填充增加载流能力2.电源输入输出不满足载流,尽量铺铜处理3.电源输出电容应该先大后小摆放4.注意确认此处是否满足载流后期自己加宽一下铜皮宽度5.注意反馈线宽走10mil即可,不用铺

扫码关注

扫码关注