- 全部

- 默认排序

同个网络怎么不能全连接

在altium Designer(AD)中,很多工程师通过使用Design Rule Check(DRC,常用于检查PCB设计是否符合设计规范和要求)功能来检查PCB设计的完成度,但很多小白不太熟悉怎么去使用DRC,下面来看看它的用法。1、

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络报表的生成。忽略ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。 图5-50 放置No E

由于有时候使用到多图纸功能,这时需要考虑图纸页和图纸页间的线路连接。在单张图纸中,可以通过简单的网络标签(Net Label)来实现网络连接;而在多张图纸中,简单的网络标签无法满足连接要求。网络连接涉及的网络标识符(如表5-2所示)比较多,

altium Designer 21全新功能差分线调节altium Designer 21对差分线的优化不可谓不大,不同于之前版本修线时不小心修动了差分线之后,阻抗间距就立即发生了变化,重新调整间距极其麻烦,基本上只能删除重画,21版本完美

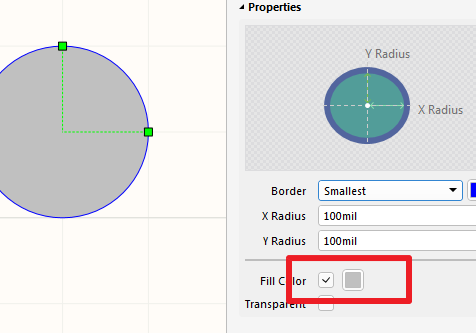

绘制实心的符号与前文中所提到的放置器件的填充的大同小异的,前者一般用于二极管或者三极管的时候,需要对那个小三角形区域进行填充,方便识别。而这一种一般是用于原理图中的测试点封装。答:第一步:菜单命令“放置”下面,直接放置。如图2.42所示。第

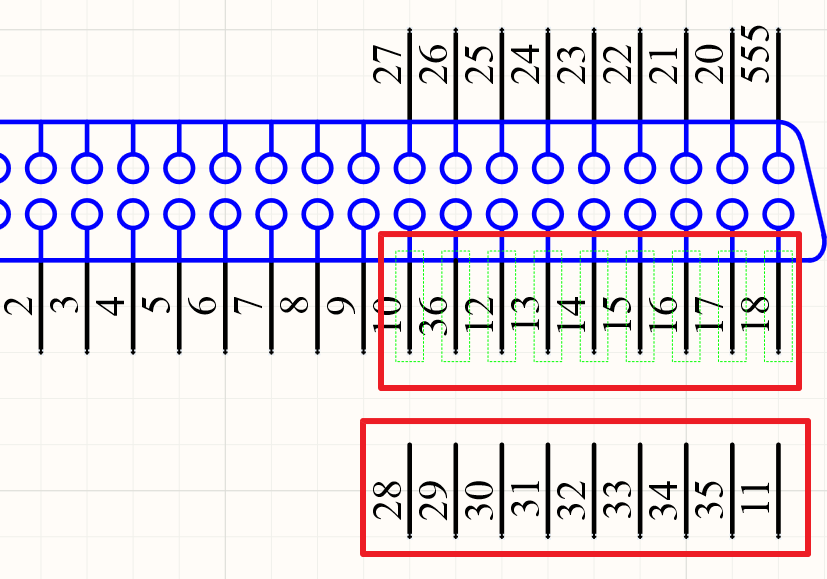

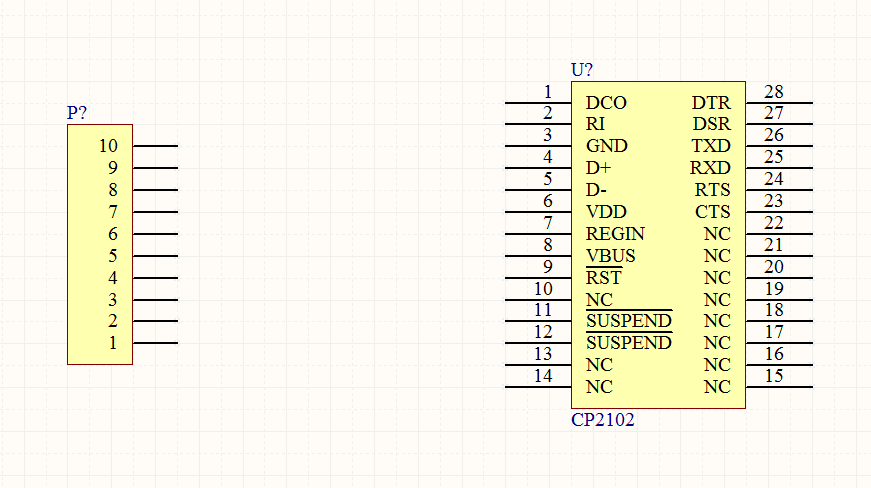

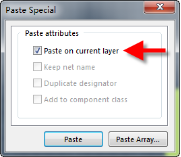

在绘制原理图原器件封装的时候,制作一个管脚特别多的原理图原器件封装。需要一个一个的模块功能分开,功能管脚需要放置到一块。运用快捷键快速的交换管脚可以省去大量的时间。以如下一个连接器为例,当我们想把框选中的这部分管脚移动到其它地方去的时候,我

在PCB设计中,绘制原理图时避免不了要用到总线,但是在我们使用altium Designer绘制总线时总是出现一些问题,导致总线无法使用。

一般不规则的焊盘被称为异型焊盘,典型的有金手指、大型的器件焊盘或者板子上需要添加特殊形状的铜箔(可以制作一个特殊封装代替)。如图27所示,此处我们以一个锅仔片为例进行说明。

EDA软件中altium Designer的兼容性是最好的,在其他EDA平台设计的原理图、PCB等文件,有时候会统一到altium Designer平台,或者将在altium Designer平台设计的文件导入其他平台,这种时候需要用到导入导出的功能。

扫码关注

扫码关注