- 全部

- 默认排序

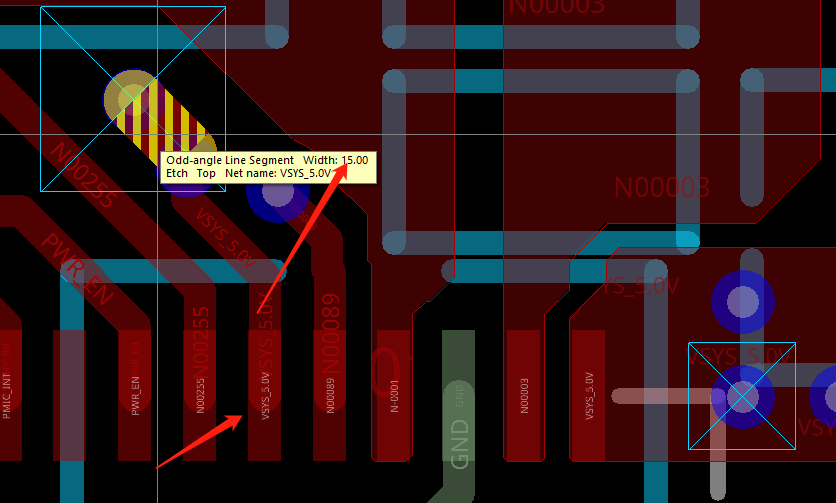

图示的线段位于这个层( Board Geometry\Outline ),红色箭头部分,要做V形切割,有如下两个疑问:1、如何将需要切割的线段(红色箭头处)表示在Art文件里?2、切割角度和深度如何表示在Art文件里?

近年来,随着超大规模集成电路工艺的高速发展,芯片工作电压明显降低,功耗逐渐增高,传输信号的提升加强,促使了电路相关设计、布局布线、叠层密度等越来越大,PCB电路自然也呈现了高速、高频传输的特性,高速PCB设计已成为未来电路设计的主流方向。在

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

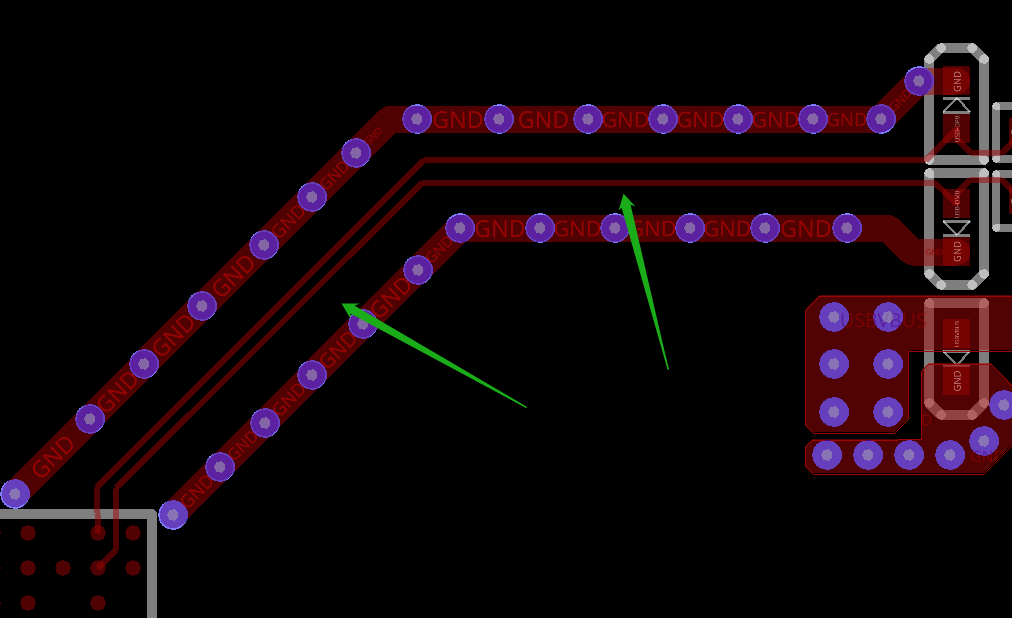

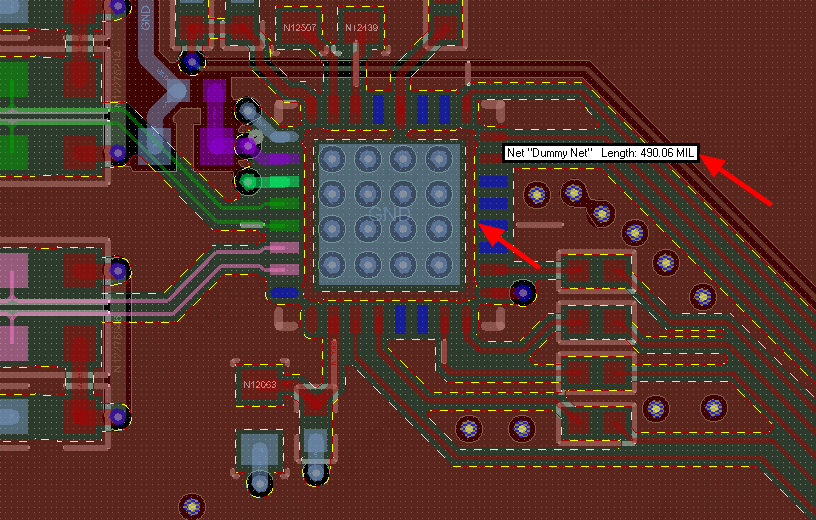

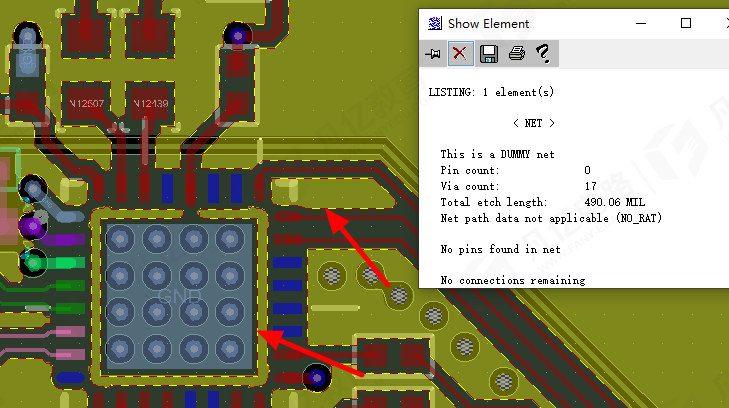

顶层大GND铜皮没有网络,多处孤岛铜皮靠近管脚放置,走线或铺铜直接连接到引脚不要接到电源层多处过孔没有网络,造成天线报错走线到过孔距离太近rx、tx分别建立等长组控100mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

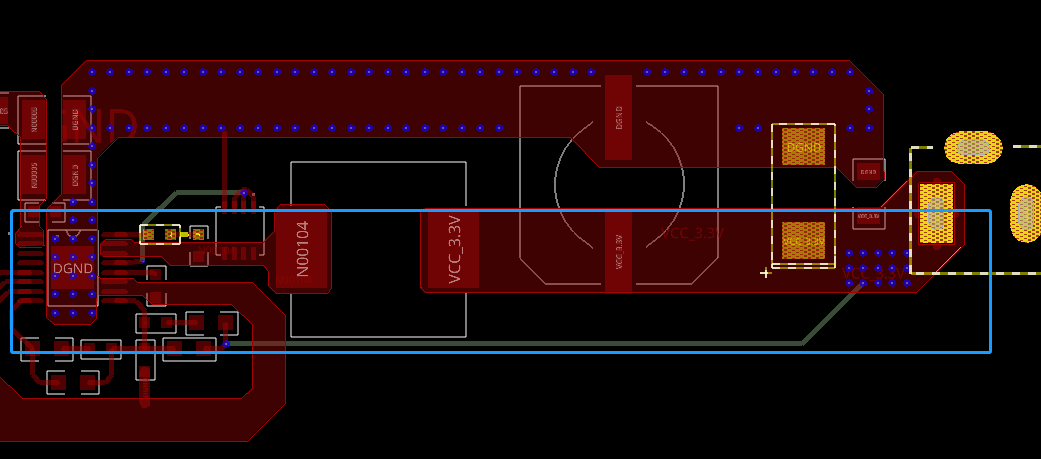

器件摆放尽量中心对齐,后期自己优化一下2.采用单点接地,只用在芯片中心打孔,其他地方不用打孔3.存在飞线未处理后期自己在底层铺铜把地网络进行连接4.反馈信号尽量远离电感,走线走10mil即可以上评审报告来源于凡亿教育90天高速PCB特训班作

大GND铜皮没有网络,导致多处孤岛铜皮靠近管脚放置,走线或铺铜直接连接到引脚不要接到电源层rx、tx分别建立等长组控100mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

此处不满足载流,后期自己铺铜处理2.反馈信号需要走10mil3.注意过孔不要上焊盘4.电源网络需要在底层铺铜进行连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://

扫码关注

扫码关注