- 全部

- 默认排序

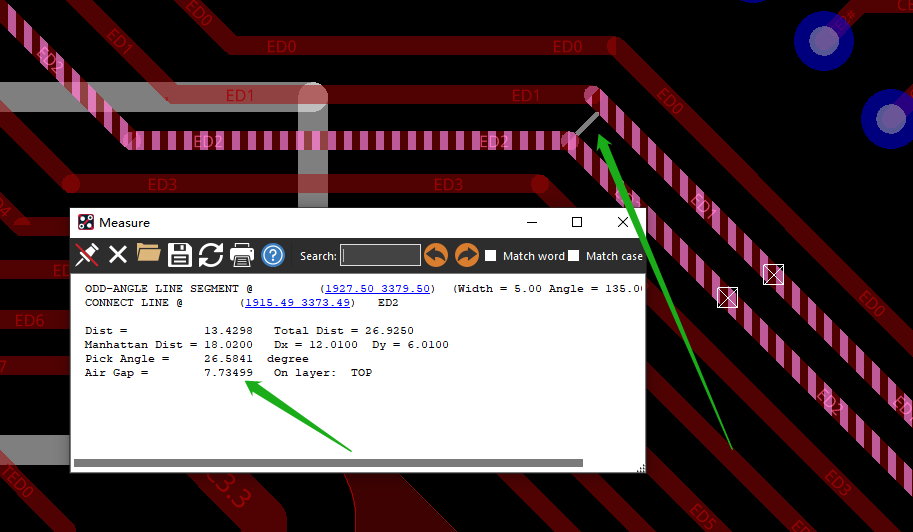

注意数据线之间等长需要满足3W间距,后期自己检查一下其他组是否满足2.注意模拟信号尽量一字型布局3.跨接间距最少要保证1.5mm,一般建议2mm,有器件的地方可以不满足4.电源输出打孔要打在最后一个电容后面5.反馈信号需要走10mil的线进

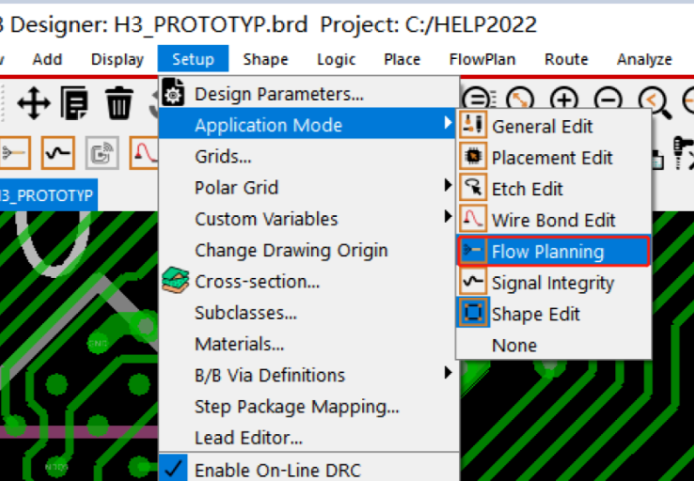

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

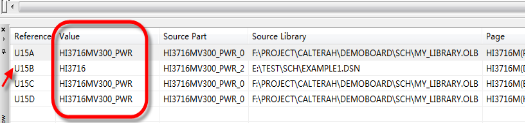

答:在使用Orcad软件输出allegro第一方网表,出现如下错误:#6 ERROR(ORCAP-36003): Conflicting values of following Component Definition properties found on different sections of U15. VALUE解决的办法如下所示:第一步,错误提示的含义是指U15这个器件分为了不同的PART,系统在进行识别的时候,属

Cadence allegro如何快速对齐器件 PCB设计过程中有一个环节是器件布局,器件的布局不但考虑电路的连通性,同时也考虑美观性,艺术性,所以器件布局尽可能整齐美观。 allegro设计PCB过程中元件的对齐这要是通过栅格对齐的方式进行器件对齐,另一是用Align components对齐命令实现对齐的。 今天教大家如何使用“Align components”对齐命令快速对齐器件,操作方法如下:

购买后联系助教拉入答疑群 随着电子技术的不断革新和芯片生产工艺的不断提高,印制电路板(PCB)的结构变得越来越复杂,从最早的单面板到常用的双面板再到复杂的多层板,电路板上的布线密度越来越高,同时随着DSP、ARM、FPGA、DDR

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

在使用allegro软件进行PCB设计过程中,大部分工程师都会使用Skill工具辅助PCB设计来提高设计效率。但是Skill工具一般都是由懂软件代码的工程师编程制作,PCB设计师一般都是只懂硬件,不知软件编程,所以对Skill的订制、使用很陌生。本次直播讲解了Skill工具在allegro软件运行的原理,讲解了allegro软件加载、运行Skill工具的一般流程,通过本次直播,能让不懂软件编程的小白迅速掌握订制Skill的一般方法。

扫码关注

扫码关注