- 全部

- 默认排序

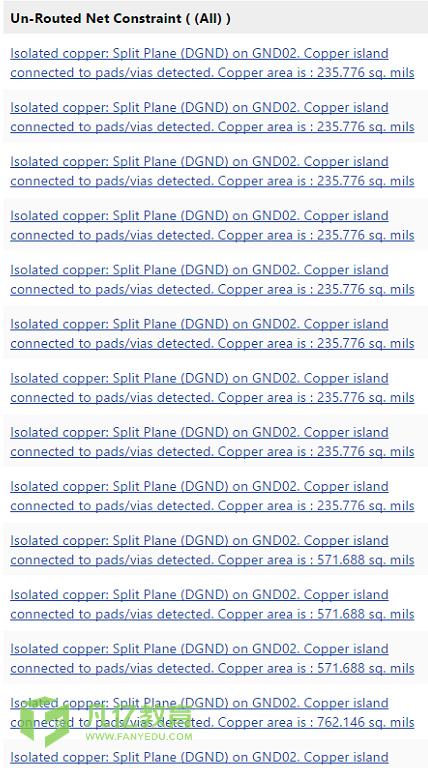

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split PLLane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

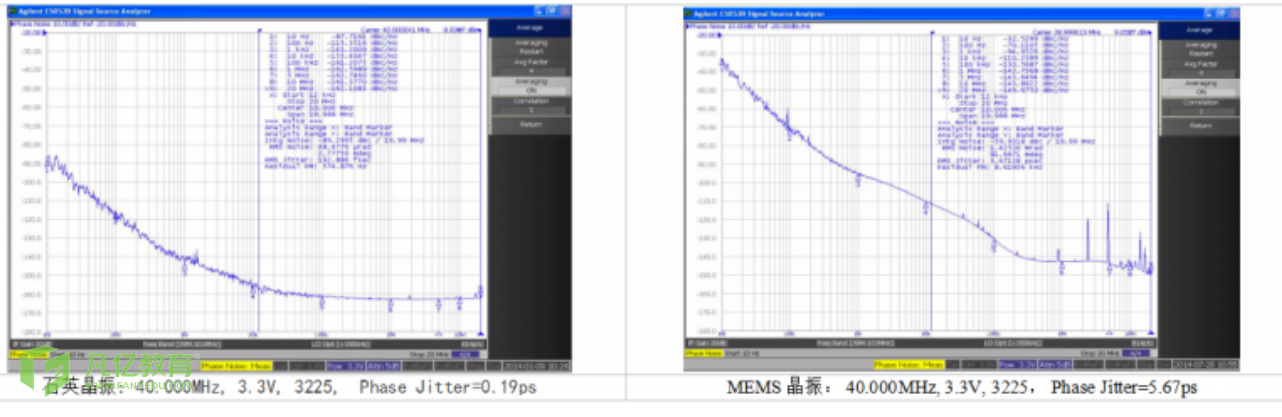

电子设备和通信系统设备的振荡器选择是影响系统性能的主要因素。目前振荡器有两种:1.石英晶体振荡器是由石英晶体的基本结构构成,和一个简单的振荡器电路。2.全硅MEMS谐振器,锁向电路,温度补偿,以及制造校准;MEMS硅晶振作为振荡源,需要PLL电路去校准频率制造公差和温度系数。MEMS振荡器更适合高振动环境,非关键定时应用以及信号噪声比不重要的应用。像高速通信,复杂调制方案,出色的信噪比之类的应用,KOAN晶体振荡器将优于MEMS振荡器。石英材质拥有低抖动,极高的Q值,以及出色的时间和温度稳定性。

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

1、直播时间2022年11月10日 晚8点直播结束后扫码添加助教领取课件备注:汪老师直播课件2、背景介绍随着无线通信技术深入研究和应用发展,在相控阵、卫星通信、雷达、电子对抗、遥测等领域,射频和微波工程正师面临着越来越大的缺口,而无线工程师供不应求已经成为了通信行业面临的重要困境。微波工程师不同于硬件工程师,射频工程师对通信理论,硬件仿真技术等有较高的要求,这也是很多硬件工程师转射频工程师难以逾越的障碍,同时也是行业中射频工程师“稀缺”的重要原因。基于此,掌握射频电路的理论和开发技术将成为每一位工程师成长的重要里程碑,同时射频电路也是迈向高薪岗位,获得更强竞争力的重要技术。3、直播能帮到用户些什么[1] 理解射频收发机的原理和架构;[2] 理解相控阵、卫星通信、雷达等微波系统的设计原理;[3] 理解ADS/HFSS软件在射频电路、射频系统开发中的应用;[4] 理解滤波器、放大器、混频器、PLL等射频器的应用和设计原理;[5] 掌握板级射频收发机系统的设计流程和设计技术。4、直播大纲[1] 射频收发机架构;[2] 滤波器、放大器、混频器、PLL等射频器的原理和设计思想;[3] 板级收发机的系统设计、器件仿真、原理图设计和微波PCB设计技术。5、课程主要讲了哪些知识点课程主要讲了零中频接收机、超外差接收机、双变频发射机的架构和板级设计技术,并详细讲解了放大器、混频器、VCO、限幅器、滤波器等射频器件的核心技术与应用。

对电子工程师来说,锁相环(PLL)是一种常见的电子电路,常用于时钟和信号处理中实现频率合成、时钟恢复和相位同步等功能,所以掌握一定的锁相环知识是很有必要的!下面聊聊锁相环的组成及工作原理。1、锁相环有哪几部分组成?锁相环由以下几个主要部分组

磁珠和磁环的区别及联系

铁氧体磁环或磁珠都可专用于抑制信号线、电源线上的高频干扰和尖峰干扰,具有吸收静电放电脉冲干扰的能力。那么磁环和磁珠的关系是怎么样的呢?今天电源滤波器小编给大家讲解一下。磁珠磁珠是一种被动组件,用来抑制电路中的高频噪声。如一些RF电路、PLL

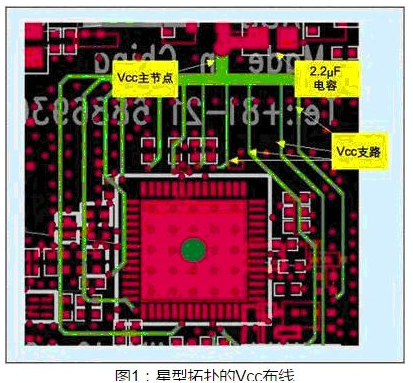

射频(RF)电路的电路板布局应在理解电路板结构、电源布线和接地的基本原则的基础上进行。本文探讨了相关的基本原则,并提供了一些实用的、经过验证的电源布线、电源旁路和接地技术,可有效提高RF设计的性能指标。考虑到实际设计中PLL杂散信号对于电源

扫码关注

扫码关注