- 全部

- 默认排序

基于良好信任,2021年7月17日凡亿教育与科曼多网络有限公司达成人才输送战略协议,为学得一技之长的电子工程师提供强有力的就业保障。此次合作,解决了企业人才短缺的现状,通过凡亿教育能快速找到专业精准的员工。凡亿又打通了“人才培养+人才输送”的一处闭环,凡亿学员也能找到自己对口并满意的工作,实现“三赢”局面。

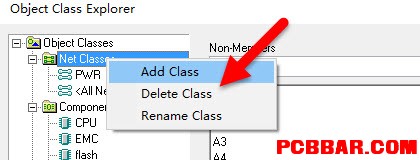

答:我们在Allegro中进行设计的时候,总会遇到这样的问题,创建类的时候,可供选择的选项太多,这里我们对这些不同的类做一个说明:

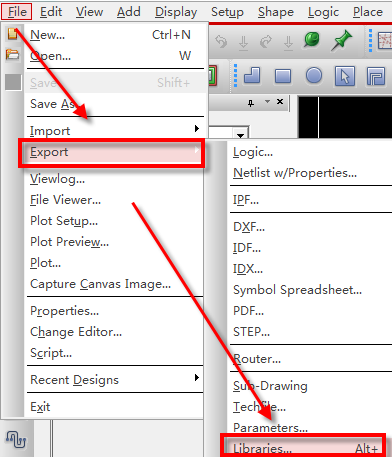

答:在导网表时,如果碰到有缺失Flash的报错,而正好缺失的Falsh在另一个项目中使用过,我们可以从另一个PCB中调用,具体的步骤如下:第一步,打开PCB,点击File-Export-Libraries…,在弹出的对话框中勾选Shape and flash symbols、No library dependencies选项,设置好导出的文件夹路径,点击Export导出,如图4-111所示;

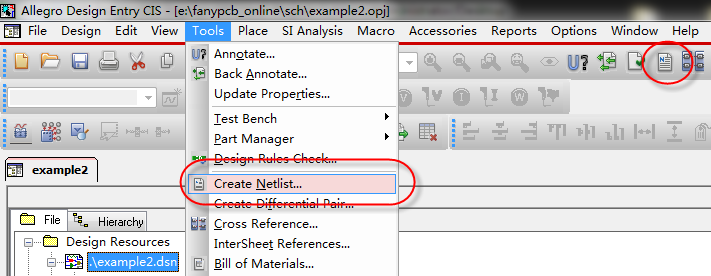

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

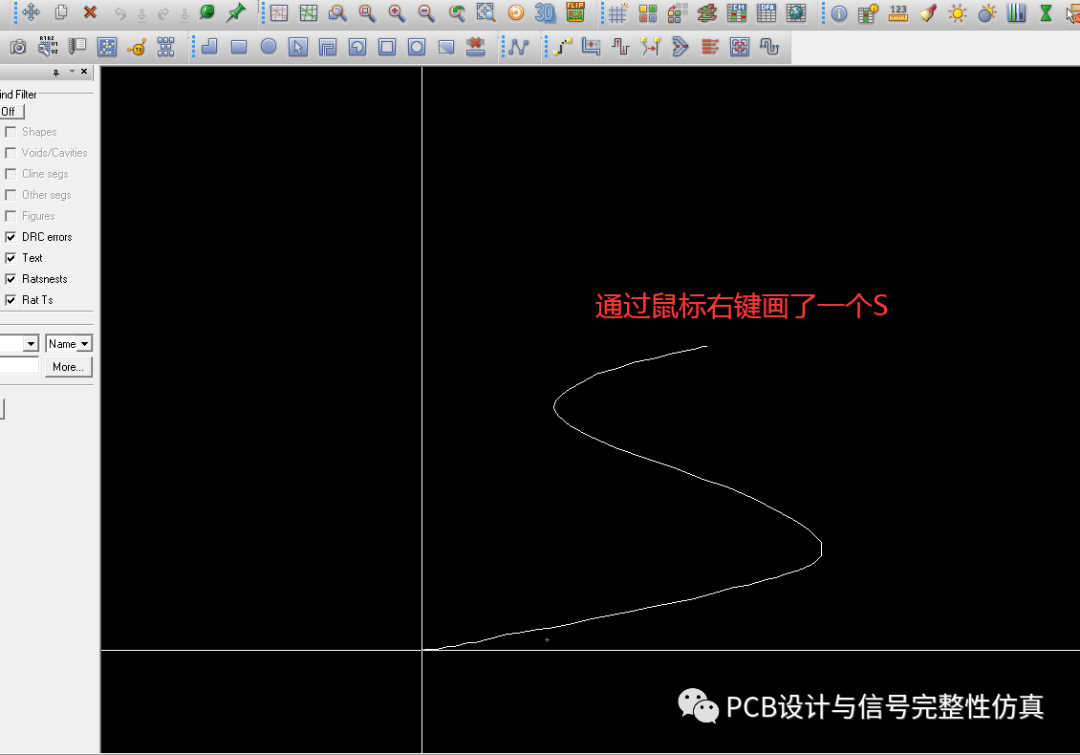

利用键盘快捷键,已经可以大幅提高设计速度。但对于使用习惯来说,通常是左手键盘,右手鼠标。因此快捷键搭配鼠标,还是需要双手进行操作。

前文对差分类的添加进行了详细的讲述,不再进行赘述,这里对差分规则设置进行讲述。差分规则设置分为两种方法,一种为向导法,另一种为手工法。

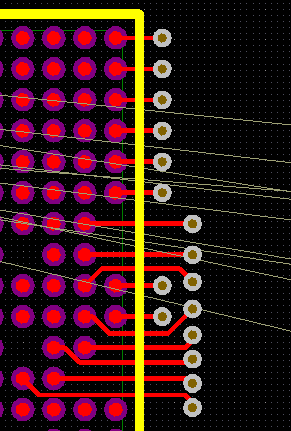

过孔随便打,不客气

在您设计PCB的过孔的时候,也需要您注意放置过孔的间距,间距最好是保证我们的两个过孔之间最少能够穿过一根线,同时在我们的规则中设置我们的内电层的保护环7mil。

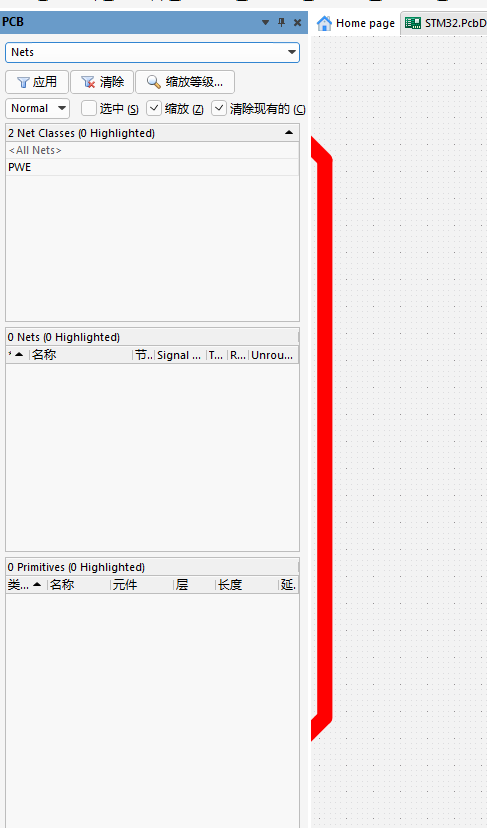

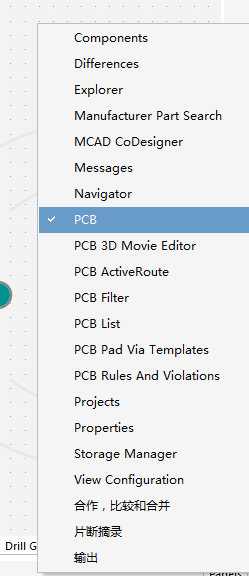

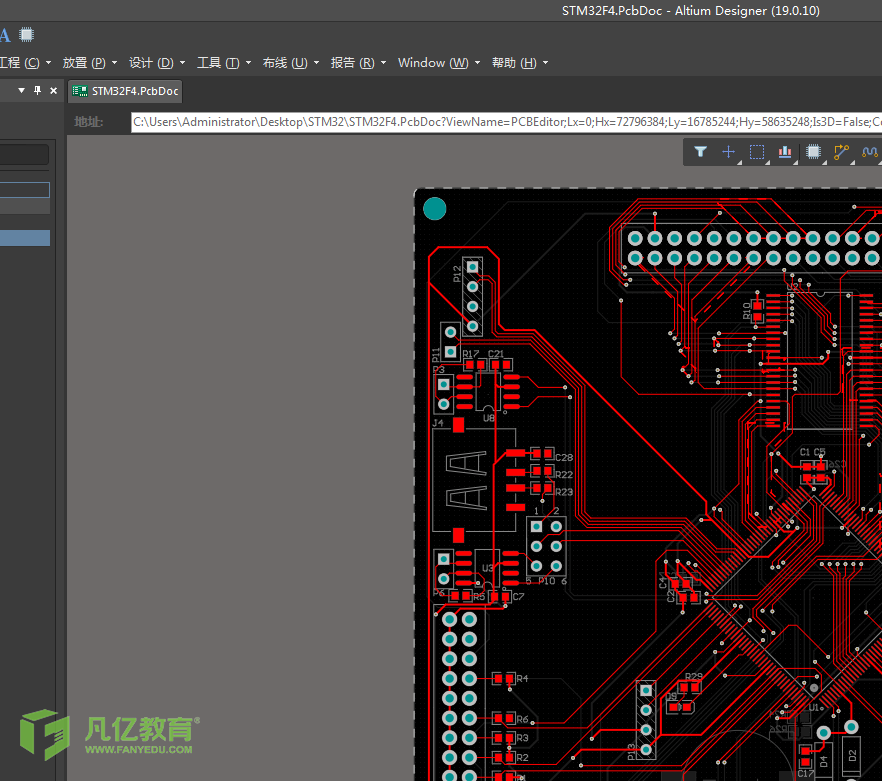

我们有时候在进行设计的时候,会缺失某些封装,那么我们如果一个一个的绘制封装的话会非常的繁琐。我们如何快速的获得封装库呢?这里就可以运用到我们的从AD的PCB中导出PCB封装库的操作了,当然了,前提就是你必须有对应的PCB才能进行导出了。

扫码关注

扫码关注