- 全部

- 默认排序

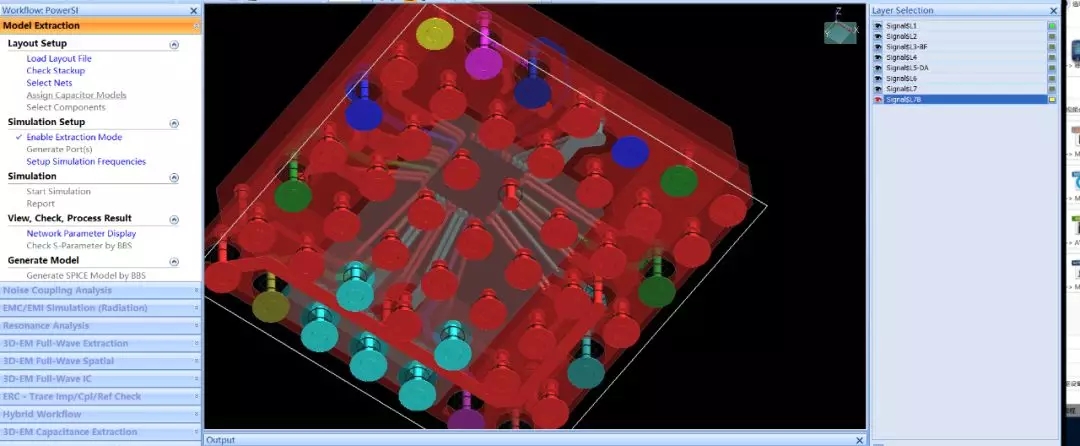

在IC封装的分析中,为了能够提取到更加趋近于真实测量结果的S参数(或者其他参数),需要在封装体上添加假性球体和参考层,下面来讲解在Sigrity™ PowerSI®工具中添加假性球体和参考层的方法。

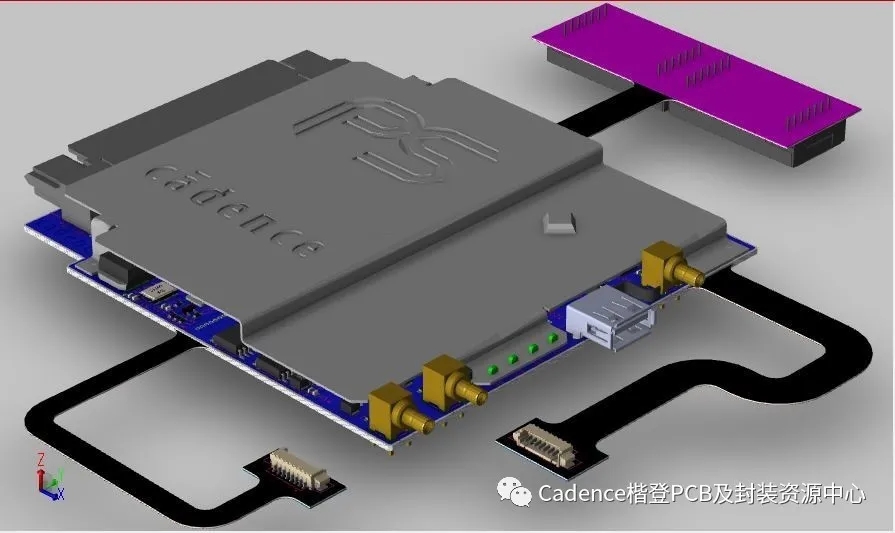

在Allegro17.4版本中,视图菜单中有两个3D绘制工具——3D Viewer和3D Canvas:

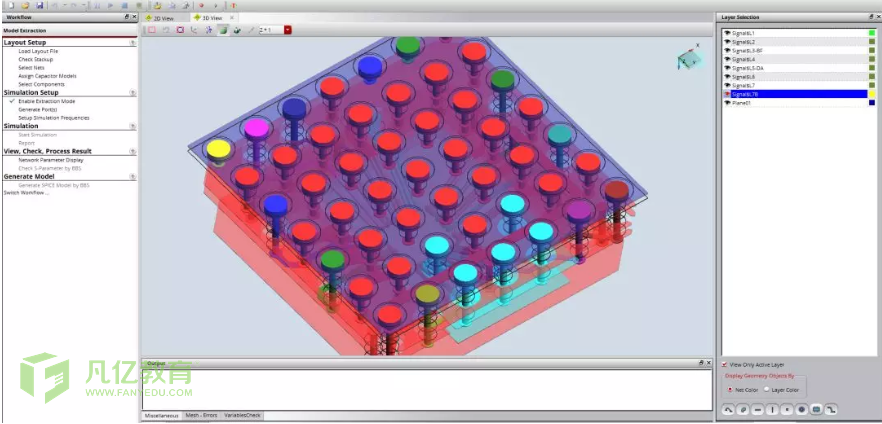

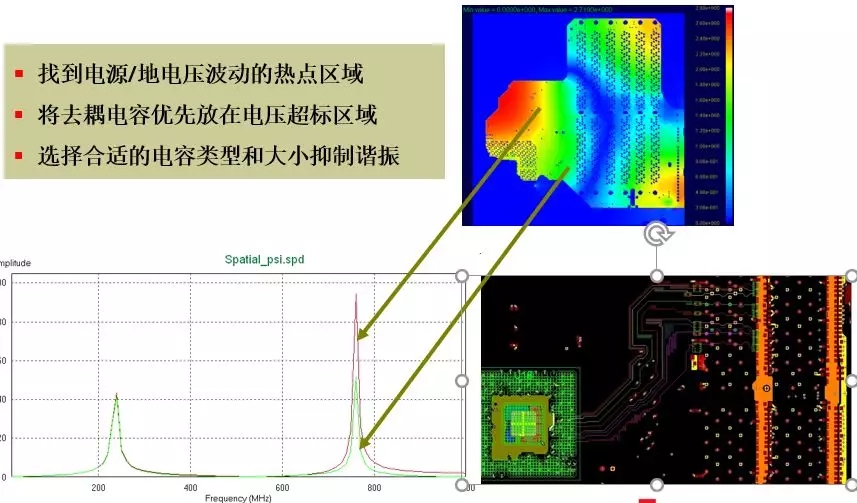

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

在IC封装的分析中,为了能够提取到更加趋近于真实测量结果的参数S参数(或者其他参数),需要在封装体上添加假性球体和参考层,下面来讲解添加假性球体和参考层的方法。

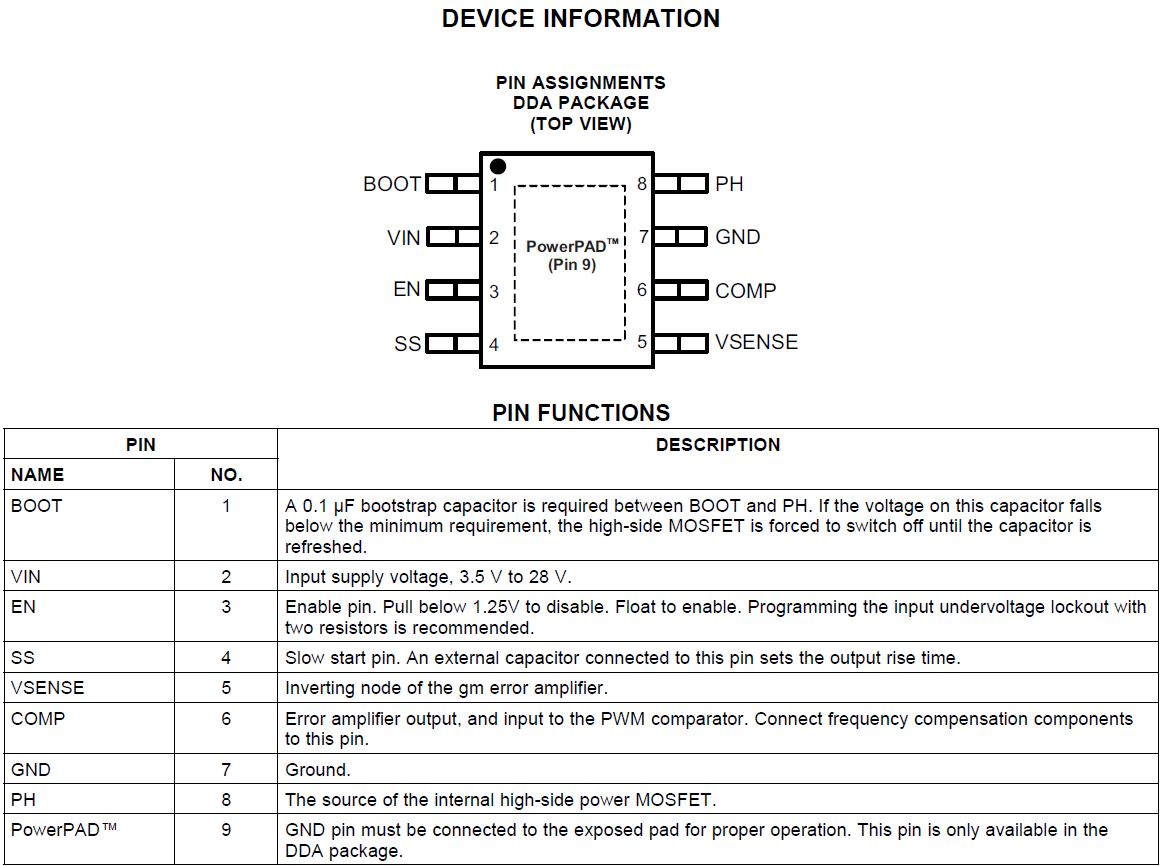

答:IC类的器件与我们讲的分立器件、逻辑器件不同,下面我们以TPS54531这个电源IC为例讲解IC器件封装创建的方法,查找TPS54531的Datasheet,它的封装信息如图2-21所示, 图2-21 TPS54531封装信息示意图第一步,在olb文件单击鼠标右键,建立新的New Part,Name那一栏输入TPS54531,PCB封装那一栏可以先不填写,下面的Parts per pkg输入1个,是单Part的器件,如图2-22所示: 图2-22&n

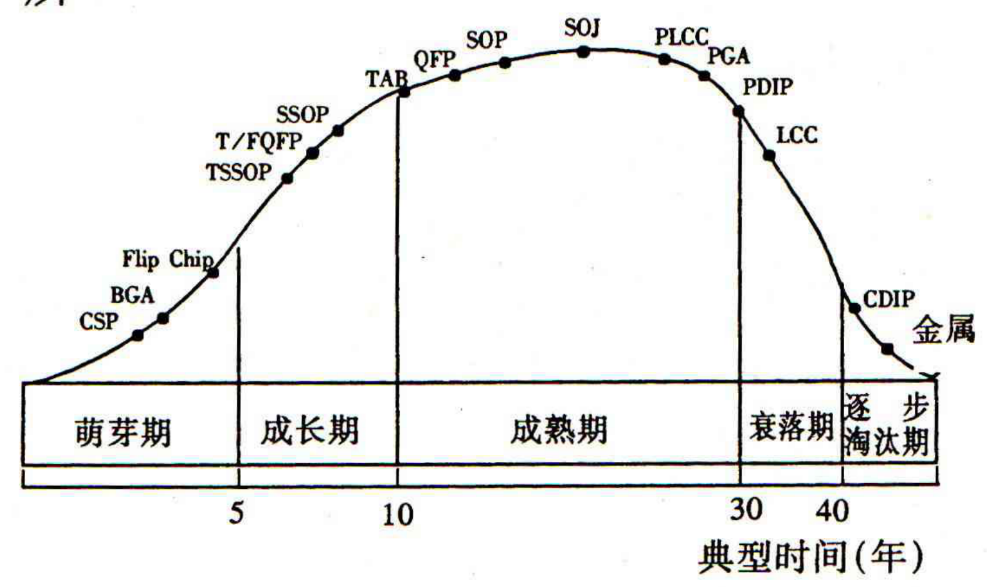

小白初学集成电路都会了解IC设计、PCB设计、电路设计,但很多小白通常会省略集成电路的封装技术,认为没有了解的必要,导致在后续的项目设计中出错,所以了解集成电路的封装技术是很有必要的,所以今天将聊聊集成电路的封装技术。1、集成电路(IC)封

随着电子设备的性能需求的日益上涨,越来越多的IC封装技术层出不穷,芯片性能大幅提升,但有很多小白不清楚IC封装技术,其中之一是晶圆制造技术,接下来我们将谈谈晶元制造技术。1、长晶长晶是从硅沙中(二氧化硅)提炼成单晶硅,制造过程是将硅石(Si

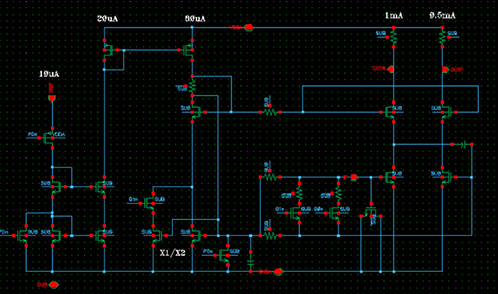

为抑制电磁干扰(EMI),很多优秀的PCB设计工程师会选择在新的设计中挑选最合适的集成电路芯片,以此达到最佳的EMI抑制的性能,同时还会将去耦电容直接放在IC封装内来有效控制EMI并提高信号完整性。但是很多小白可能不太清楚IC封装的EMI控

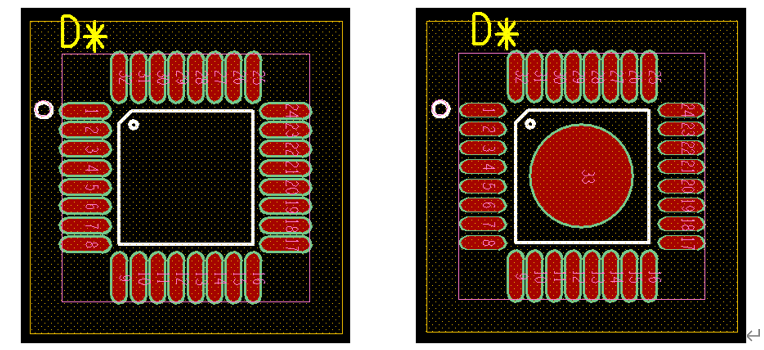

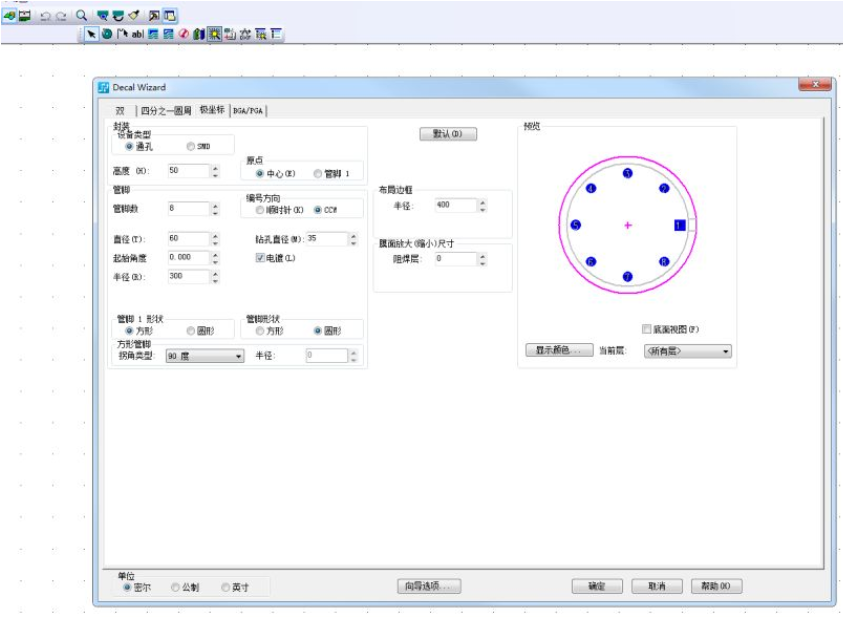

创建BGA IC封装也是可以使用PCB封装向导去进行设置创建。1、点击“绘图工具栏”图标,弹出对应的分列,点击“向导”,弹出“Decal Wizard”对话框,如图1所示。图1“Decal Wizard”对话框2、然后点击左上角的BGA/P

扫码关注

扫码关注