- 全部

- 默认排序

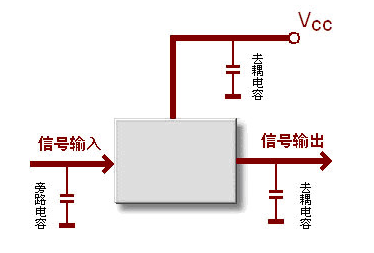

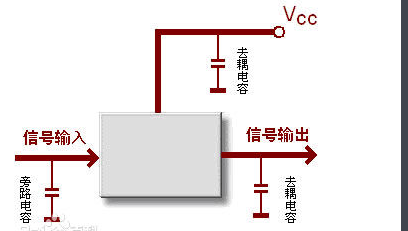

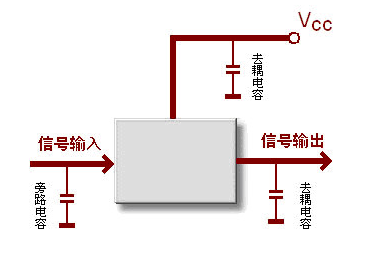

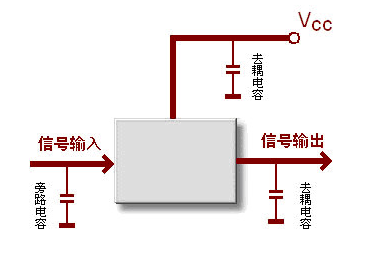

滤波电容:在电源整流电路中,用来滤除交流成分,使其输出的直流更加的平滑。 去耦电容:在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。 旁路电流:在电阻连接时,接在电阻两端使交流信号顺利的通过。(1)关于去耦电容蓄能作用去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,而器件V

旁路电容与去耦电容的区别

可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。 去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。 去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹

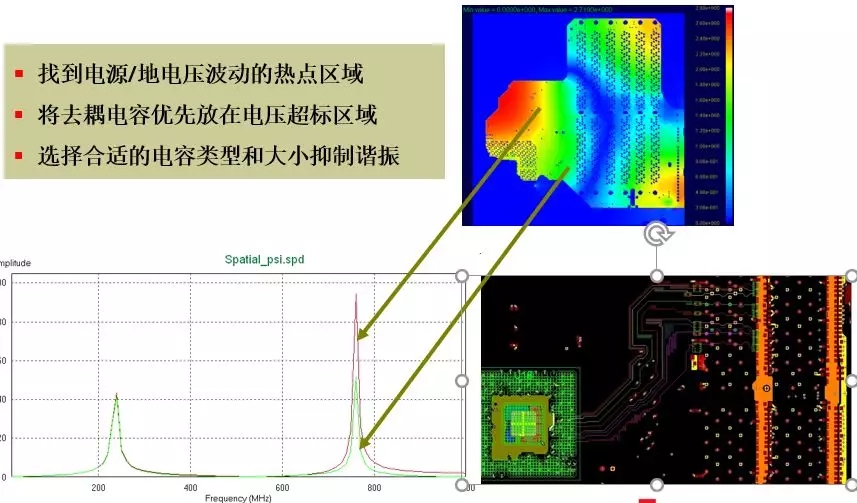

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

电源往往是我们在电路设计过程中最容易忽略的环节。其实,作为一款优秀的设计,电源设计应当是很重要的,它很大程度影响了整个系统的性能和成本。

答:可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。 去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电

答:可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。

通过一次关于基本知识的对话,让我们深入考察那没有什么魅力但是极其关键的旁路电容和去耦电容。旁路电容是关注度低、没有什么魅力的元器件,一般来说,在许多专题特写中不把它作为主题,但是,它对于成功、可靠和无差错的设计是关键。来自Intersil公

今天的许多设计都包括三个不同值的去耦电容器,或者当只使用一个电容器时,可以使用 0.1 uF 这样的小值。这些建议基于 50 年前不适用的假设。是时候重新考虑这些过时的遗留设计指南了。作为遗留问题的神话从一开始,电子行业就被更快、更小、更便

扫码关注

扫码关注