- 全部

- 默认排序

在FPGA设计时,我们总会遇到各种各样的设计难题,并发愁如何解决,所以小编将搜集网络上九个小白最头疼的FPGA设计问题,并进行回答,希望对小白有所帮助。1、如何控制XST插入buFFEr?①用buFFEr_type约束,具体使用方法在XST

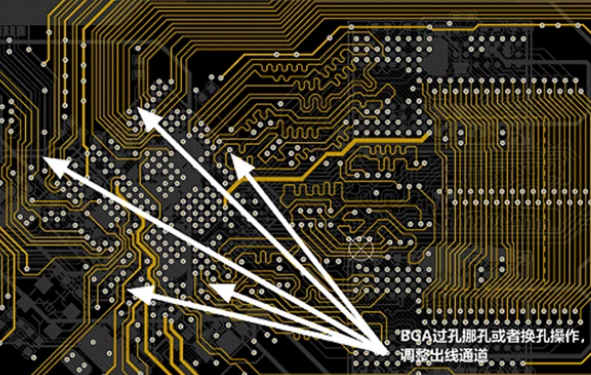

在高速PCB设计中,差分信号(DiFFErential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。布线要

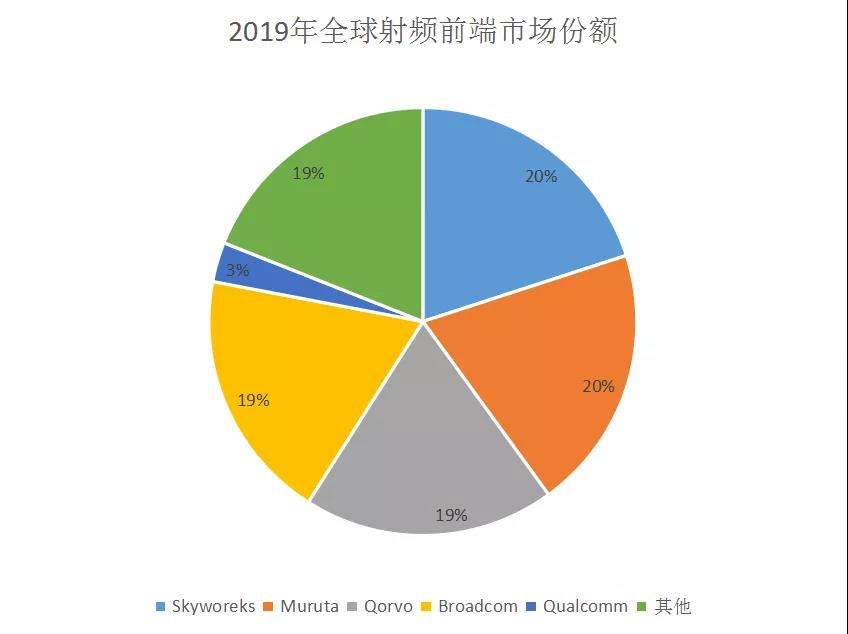

射频前端(RFFE)作为模拟芯片这顶皇冠上的“明珠”,如今随着5G技术的全面铺开,全球的市场格局正在发生悄然变化。据高通数据统计预测,三年内5G射频前端市场复合增长率为12%,规模将达到180亿美。

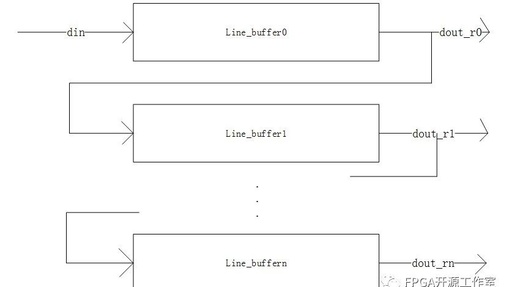

FPGA图像处理之行缓存(linebuFFEr)的设计一背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。FPGA实现图1 行缓存菊花链

IPQ5018, 802.11ax,wifi 6e,QCN9074,2X2 2.4G support 2x WiFi 6E Card support BT5.1 IPQ6000/IPQ6018/IPQ6010/IPQ4019/IPQ4029

60天PCB高阶特训,从菜鸟到就业一站通关,先人一步拿下高薪oFFEr。加入60天高阶特训班,帮你避免没效果、没目的、没方法的盲目学习!

LVDS原理及布板技巧

LVDS: 低电压差分信号LVDS(Low Voltage DiFFErential Signal)即低电压差分信号。LVDS的特点是电流驱动模式 电压摆幅350mV加载在100Ω电阻上。其中发送端是一个3.5mA的电流源,产生的3.5mA

差分布线怎么连接两端?

定义了差分对以后,采用 DiFFErential Pair Routing开始布线,可是一边的两个焊盘走线总是连不上另外一边的两个焊盘 ,这种情况怎么解决呢,大佬

扫码关注

扫码关注