- 全部

- 默认排序

在PCB设计过程中,Pads是一个广泛使用的EDA软件,经常应用在国内外大型项目,Pads软件按其工作模式提供了三种工具软件,分别是Pads Logic、Pads Layout和Pads Router,今天我们来讲讲他们的不同用法及区别。1

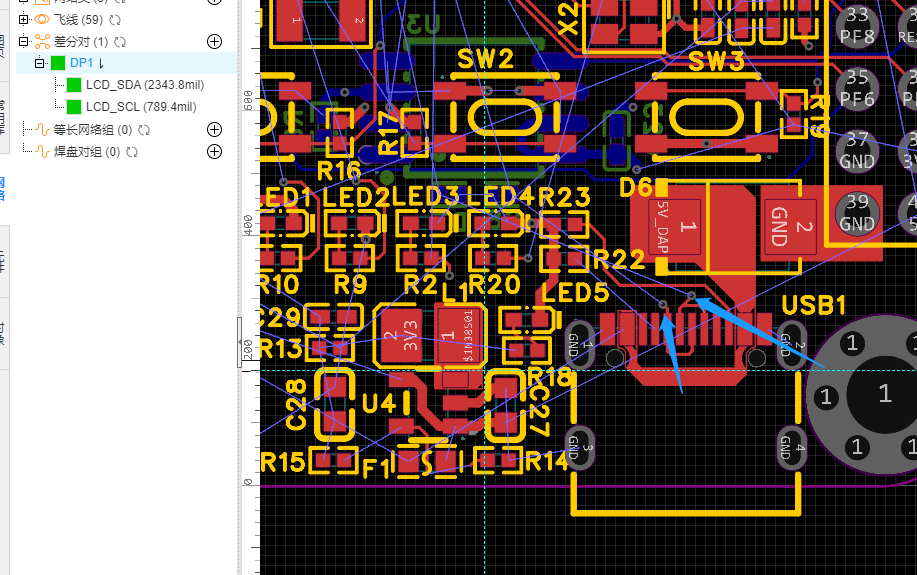

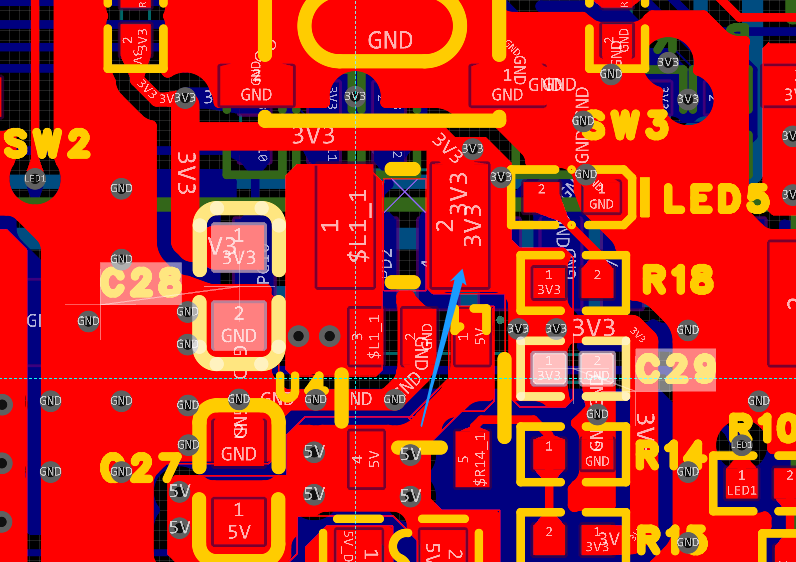

USB信号需要创建差分对2.电源输入的滤波电容应该靠近输入管脚(4脚)放置3.优先晶振走线,靠近IC放置,走类差分形式,并包地处理,晶振下面不要走线4.器件摆放尽量对齐处理后期把线连通,等长完后在进行评审

差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍2.器件摆放尽量对齐处理3.晶振走线需要走类差分处理4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.此处在一层走线即可,建议铺铜处理6.时钟包地需要在地上间隔150mil-200m

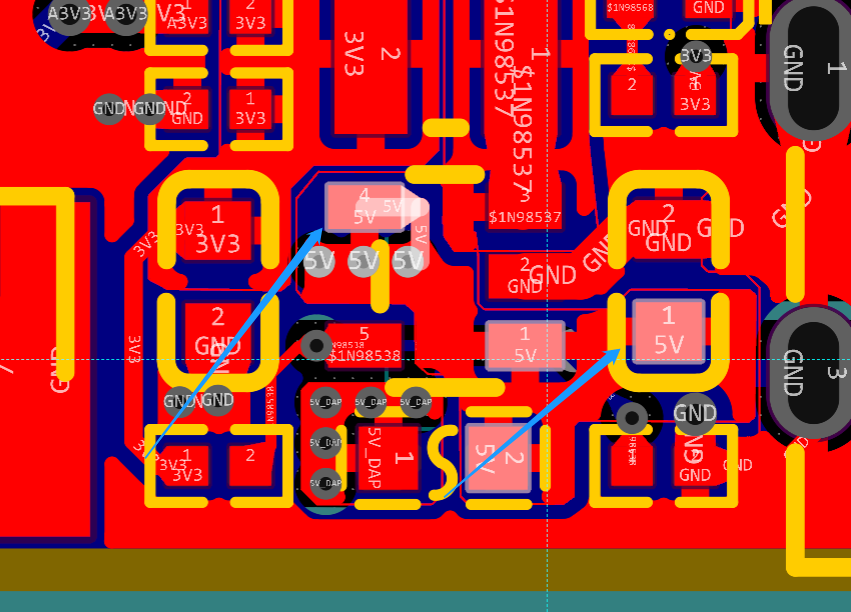

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

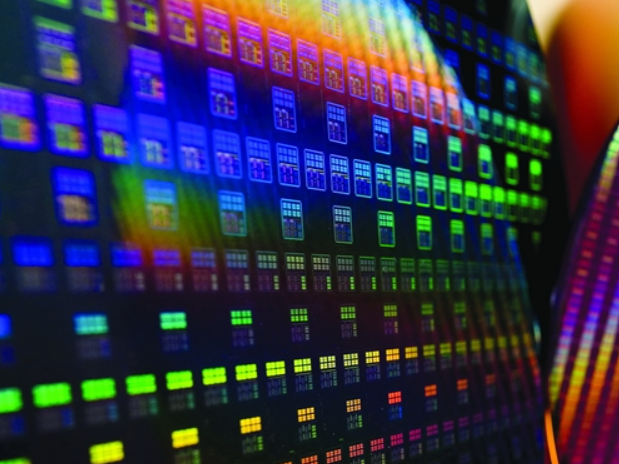

随着科学研究与技术开发市场化,采用传统电子设计手段在较短时间内完成复杂电子系统设计,已经越来越难完成了。EDA(EleCTRonICs Design Automation)技术是随着集成电路和计算机技术飞速发展应运而生一种高级、快速、有效电

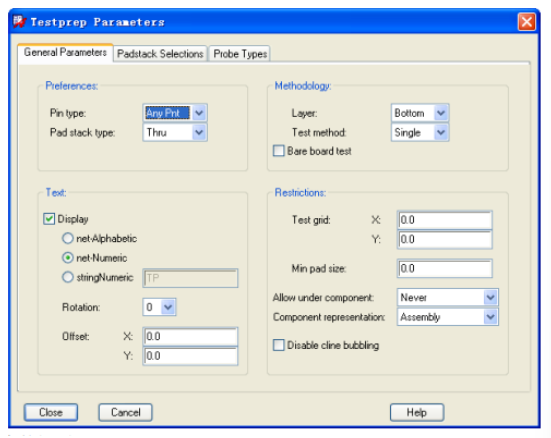

Allegro因其功能强大、界面灵活、可适应切换复杂项目的需求,很快成为全球最受欢迎的EDA软件之一,而很多工程师在Allegro软件中添加测试点,这样做的好处是为了进行电路的功能测试和故障诊断,那么如何在Allegro添加/生成测试点?下

电源输出的滤波电容要靠近输出管脚放置2.USB的电容放置不到位,应该线经过电容在连接到USB器件,差分出线要耦合出线,走在一起3.器件干涉4.SDRAM的滤波电容尽量保证一个管脚一个5.顶底层器件干涉,顶层器件是插件,你底层也放器件,后期不

5月6日,全球知名EDA及半导体厂商新思科技(英文名:Synopsys)宣布已经与Clearlake Capital和Francisco Partners领导的私募股权财团达成最终协议,将以21亿美元(约151.61亿人民币)出售其软件完整

Altium Designer(简称AD)是一款广泛应用电子设计的EDA软件工具,在使用AD过程中可能会遇见“希望在PCB板上添加中文汉字”的需求,那么针对这个需求如何做?1、打开AD软件,新建一个电路设计项目;2、在新建项目中,选择“Op

扫码关注

扫码关注