- 全部

- 默认排序

DDR5规范文档下载

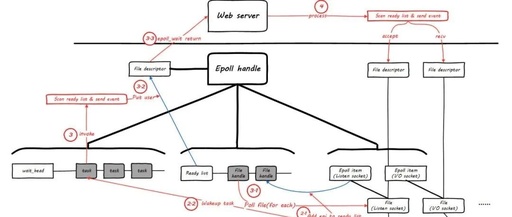

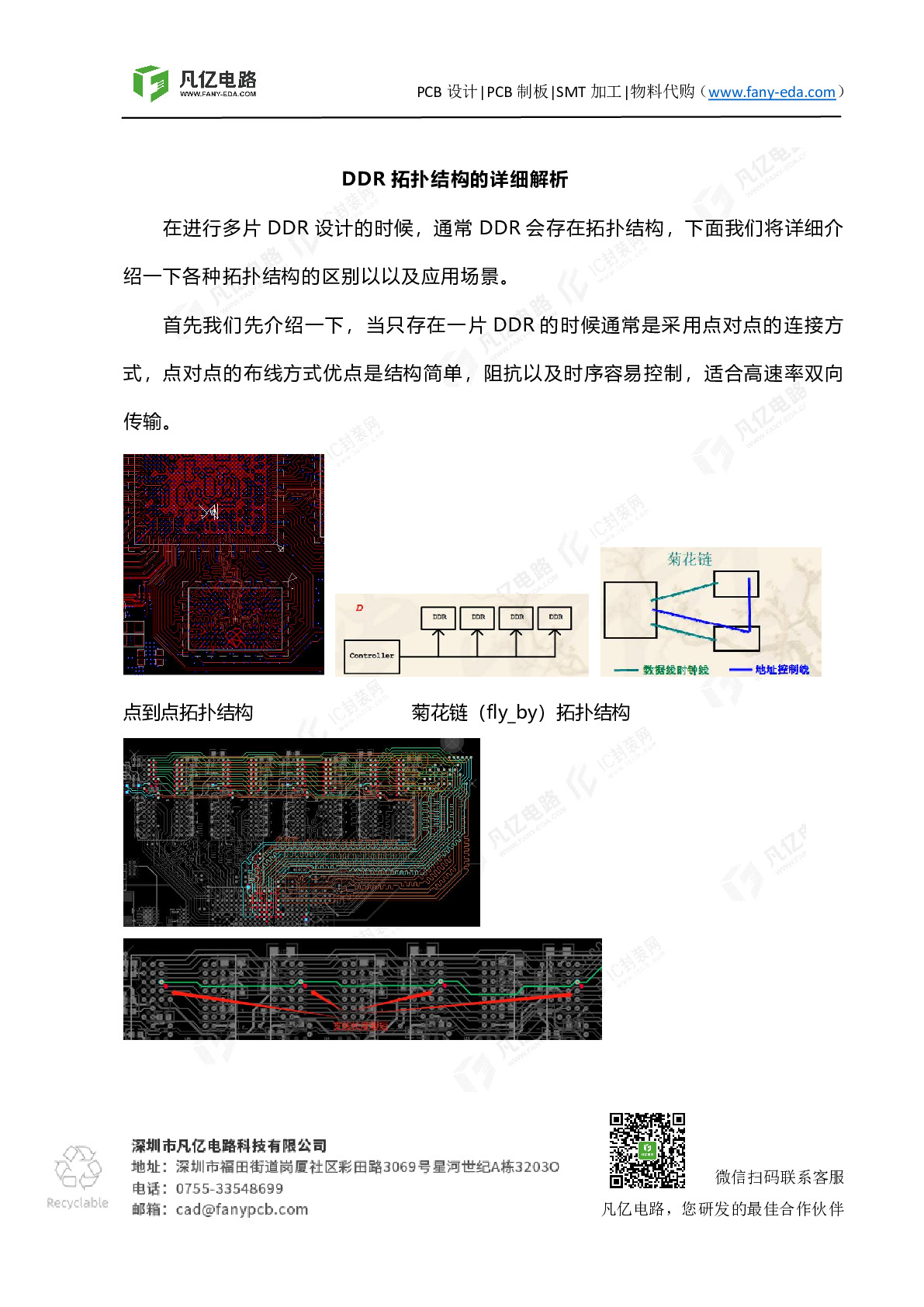

hello, 大家好,我是Alex,今天分享一篇关于socket编程里面经典问题:惊群问题,文章深入分析了惊群问题的现象和其根本原因,并给出一些很好的解决方案,值得我们参考和学习,通过文章,我们可以学习到彻底理解惊群问题epoll底层实现原理epoll的ET和LT区别socket的reuseaDDR

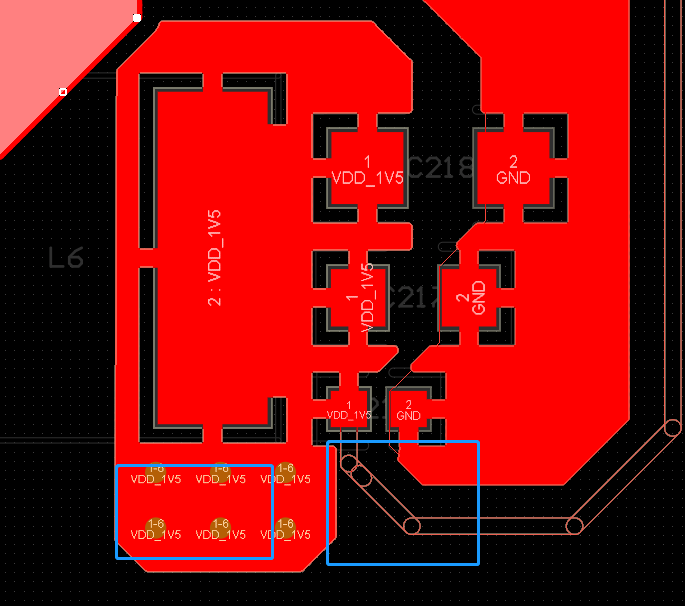

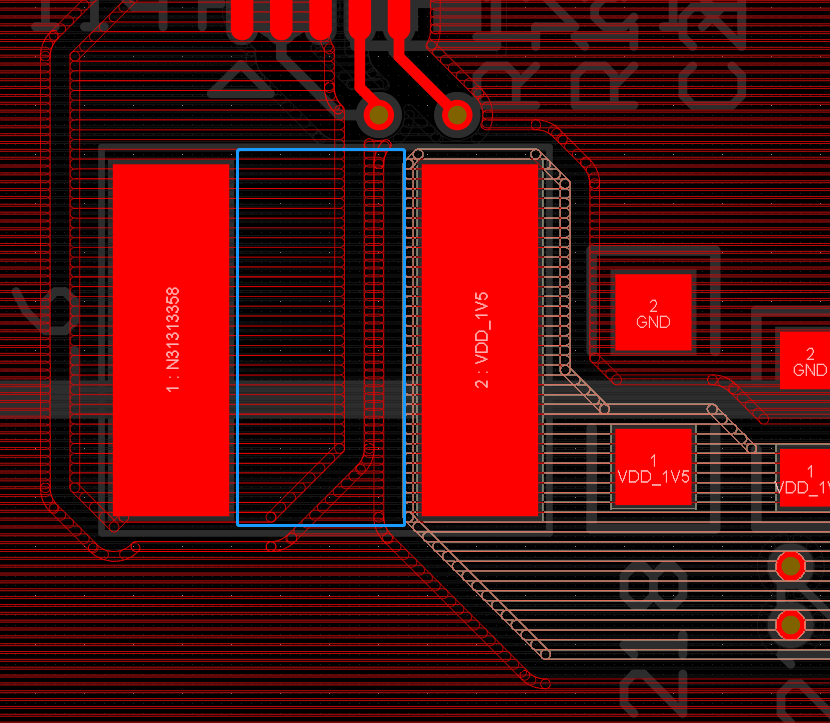

电源输出打孔要打在电容后面2.反馈信号要走10mil3.等长存在误差报错4.差分走要满足差分间距要求,等长原则是哪里不耦合,就在哪里进行等长5.VREF线宽最少要加粗到15mil以上6.注意器件摆放不要干涉以上评审报告来源于凡亿教育90天高

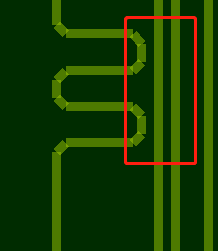

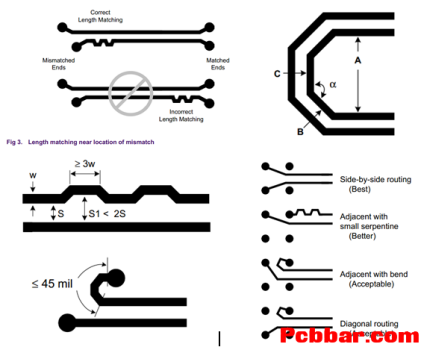

数据线线距不满足3w这里差分等长间距不能大于2Svref离数据线太近了以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.ht

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

一、产品问题描述某车载产品进行EMC测试,发现1.6GHZ处超标,不能满足标准要求。① 远场测试图 图 1 远场测试图② 测试结果注:由上图测试结果可见,受测样机辐射发射骚扰测试在1600MHz频点存在超标情况,超标数值为5.34DB。二、定位与初步分析经与客户沟通得知样机内DDR通讯的时钟信

DDR5内存都来了,DDR3内存是不是要彻底退出历史舞台了?那得看什么应用场景。华邦电子今日宣布,将在未来10多年内继续供应DDR3 DRAM内存芯片产品,并且会持续扩产,以确保满足客户的长期使用需求。目前,DDR3出货量占华邦DRAM总收

电感所在层的内部需要挖空处理2.反馈线走一根10mil的线即可,不用进行铺铜3.存在开路4.地址线等长存在报错5.注意电源线宽尽量保持一下,满足载流,走线最少需要加粗到15mil以上6.地网络需要就近打孔以上评审报告来源于凡亿教育90天高速

扫码关注

扫码关注