- 全部

- 默认排序

老师,这是为什么?找了好一会了,

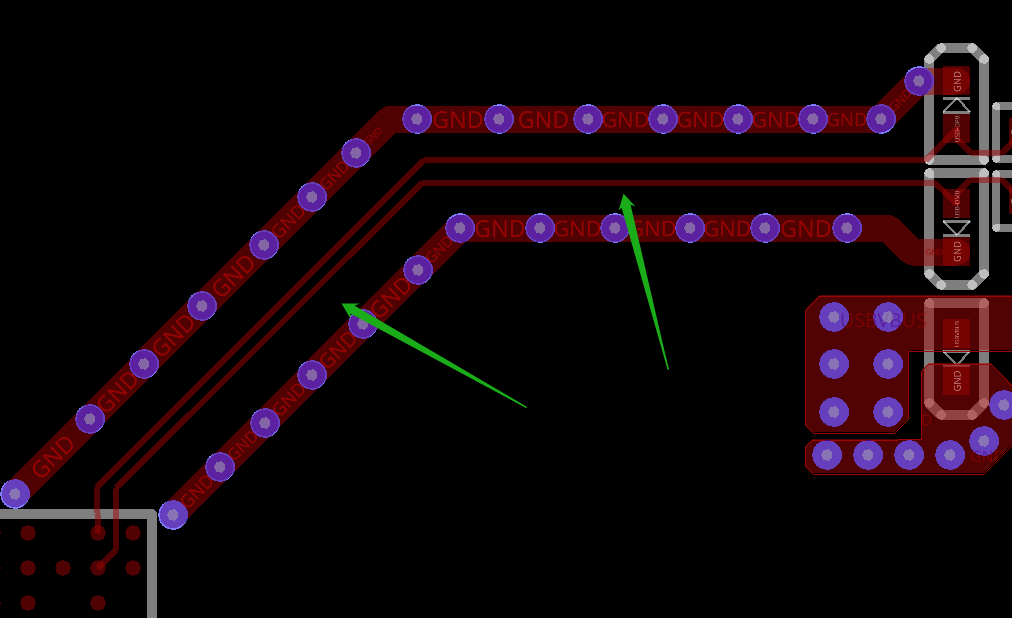

USB2.0:差分走线是需要保持耦合,需要修改,不合格:USB3.0:还有一块铜皮存在板外,自己删除下:此处器件注意整体中心对齐放置:差分信号打孔换层的过孔两侧打上地过孔:此处差分需要优化,要耦合走线 :注意此处焊盘出线,需要从两侧边拉线出

有人说,公司招聘员工进来工作,支付报酬,员工自然有义务为公司提供相应的价值,那么去掉工作之外,公司有必要给员工提供岗位技能培训吗?答案自然是显而易见,尤其是对于很多正处于创作疲倦期的电子工程师来说,更无需单独领出来发问!公司正常招人,不能奢

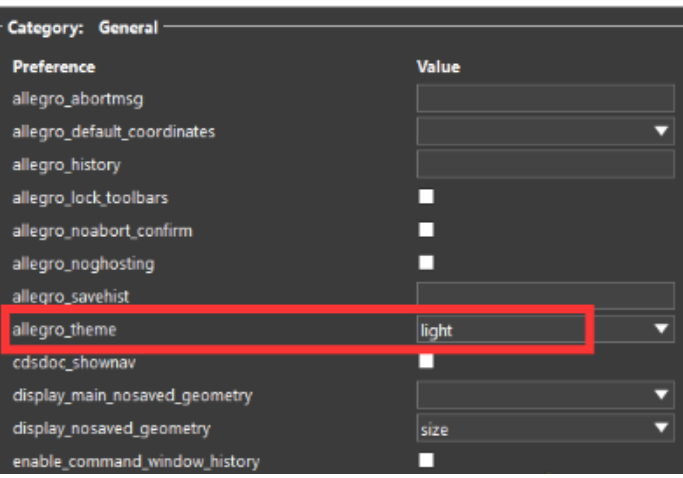

在电子工程师的日常工作中,长时间面对PCB设计软件是很容易带来眼睛疲劳等问题,为了提高工作效率,很多工程师选择将软件界面切换为暗黑模式,该模式提供了更舒适的视觉体验,特别是在低光环境下或长时间使用的情况下,那么在Allegro 17.4版本

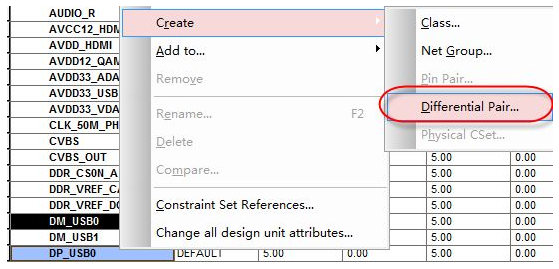

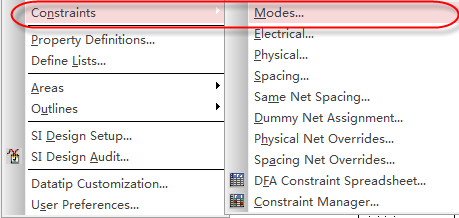

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加一、手动添加差分对:1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

扫码关注

扫码关注