- 全部

- 默认排序

对电子工程师来说,在使用Altium Designer进行团队协作时,域控制器之间的幅值是至关重要,但在使用过程中很容易遇见域控制器之间复制失效的问题,导致团队协作困难,设计效率大大降低,面对这种情况该如何找到原因并解决问题?1、AD域控制

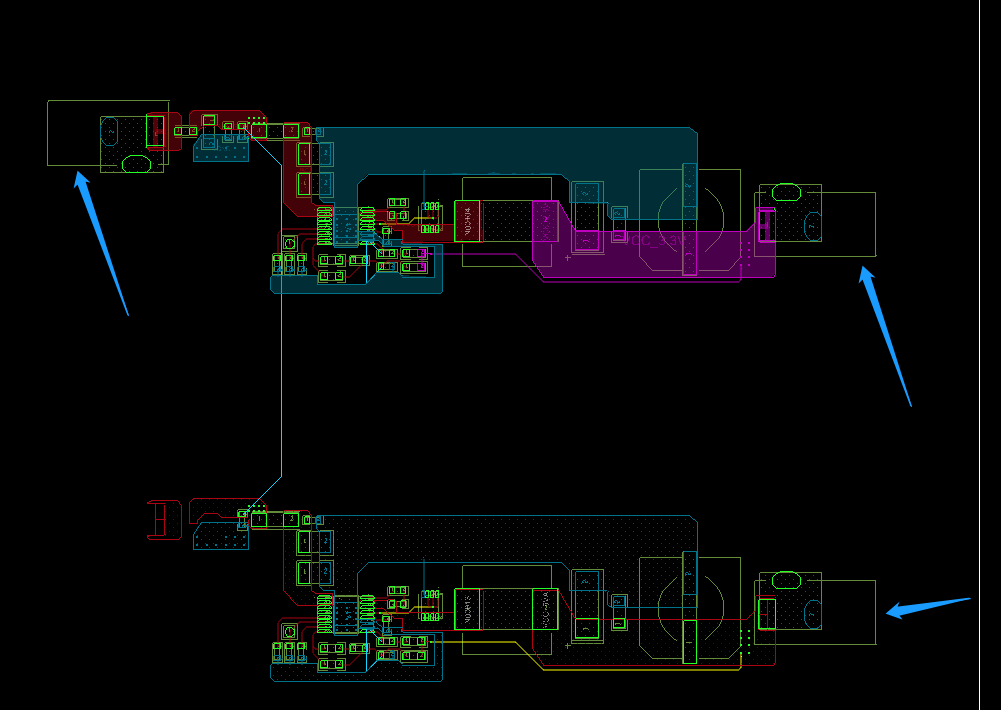

PCB的叠层设计在电子产品的开发中起到非常重要的作用,正确的叠层设计可明显提高信号完整性、降低电磁干扰,提升功耗效率等,然而PCB叠层设计并非那么容易好做,下面来看看想设计好PCB叠层该注意哪些方面?1、确定叠层层数在进行叠层设计前,先确定

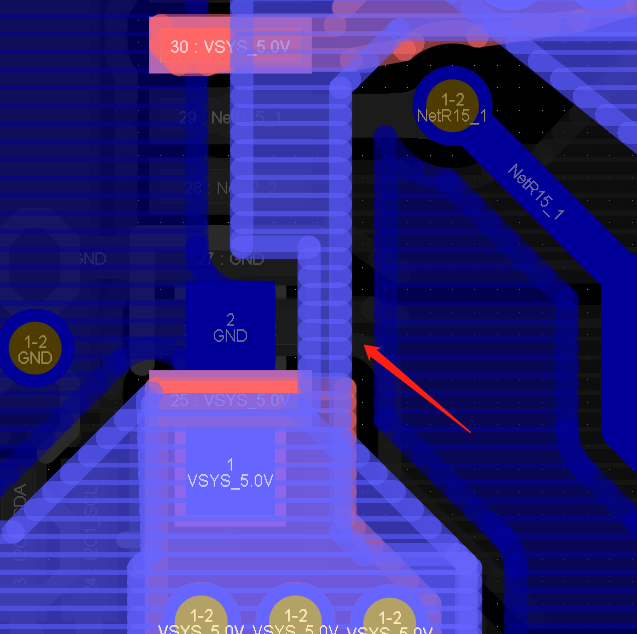

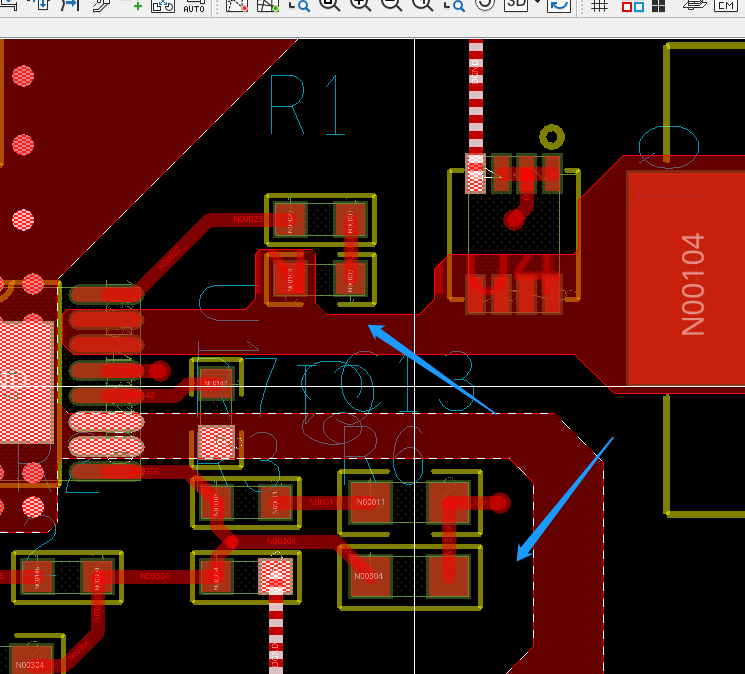

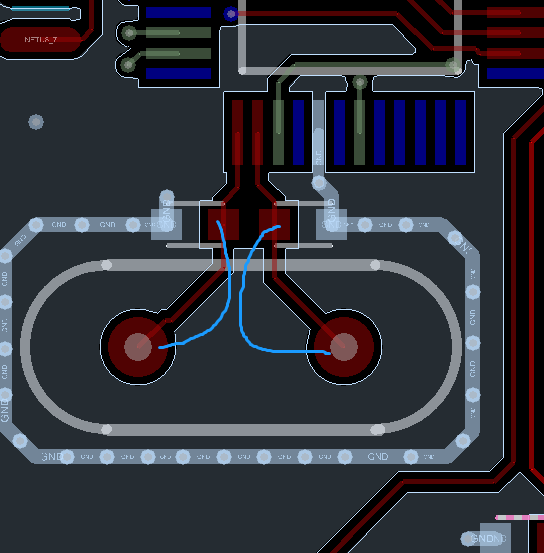

此处出现载流瓶颈2.注意电感底部不要放置器件以及走线,需要重新优化下底层的布局以及布线:3.走线与焊盘同宽,拉出在进行加粗处理4.反馈线走10mil,走线远离电感以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

配置电阻电容注意布局可以向下向上放置,中间腾出空间优先放置主干道上的器件:主干道上的器件布局优先级最高。建议吧静态铜皮转换为动态铜皮,设计基本放置动态铜皮:反馈信号走个8-12mil即可:注意器件丝印最好调整下,不要重叠了:注意同焊盘网络连

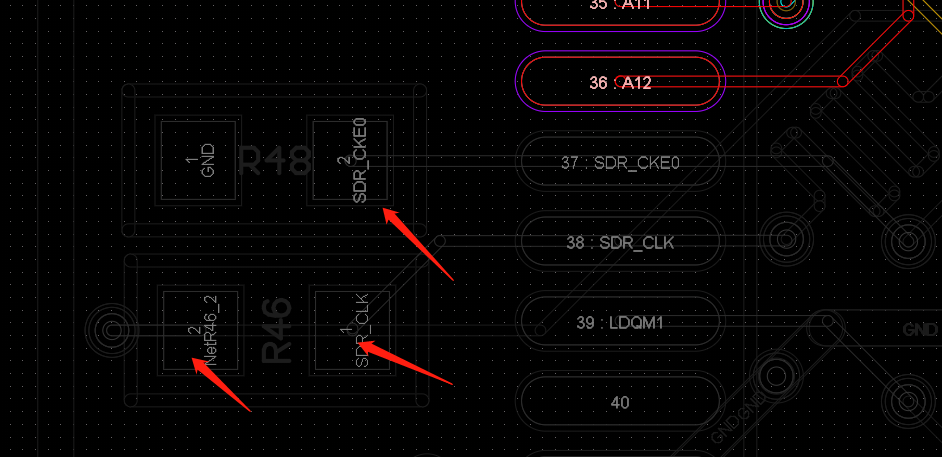

晶振走内差分需要再优化一下2.地分割间距最少满足1mm3.锯齿状等长不能超过线距的两倍4.网口除差分线外,其他的都需要加粗到20mil5.模拟信号尽量一字型布局6.电感所在层的内部需要挖空7.反馈需要从最后一个电容后面取样8.数据线和地址线

型号:VK1C21C LQFP44品牌:永嘉微电/VINKA封装:LQFP44年份:新年份工程服务,技术支持,原厂优势。概述VK1C21C是一个点阵式存储映射的LCD驱动器,可支持最大128点 (32SEGx4COM)的LCD屏,也支持2C

Pads Layout属于Mentor Pads软件的子工具,以外偏重于自动布局,一直以来被工程师广泛应用在各种电子产品的研发上,但在使用过程中,有没有技巧可以帮助提高效率,优化产品性能?下面来看看吧!1、避免布线错误在布线过程中,错误的布

地址线分组,CLK,CKE0都要添加进来一起进行等长2.数据线分组应该是一组9根2SDRAM注意规则设置,导致等长有黄色提示2.注意过孔需要盖油处理其他没什么问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

步入21世纪后,在5G、人工智能、大数据等新兴技术的推动下,射频微波产业开始成为国家优先发展的重要战略产业之一,这也要求很多电子工程师具备一定的射频微波知识,下面将谈谈射频微波的基础知识,希望对小伙伴们有所帮助。一般来说,射频微波是指频率在

座子需要靠近板框放置2.滤波电容放置要保持先大后小原则3.反馈线需要走一根10mil的线4.打孔要打在滤波电容的前面5.电源主干道需要再底层铺铜进行连接,不要有开路6.走线尽量不要有锐角7.电感下面尽量不要走线,反馈尽量远离电感,电感所在层

扫码关注

扫码关注