- 全部

- 默认排序

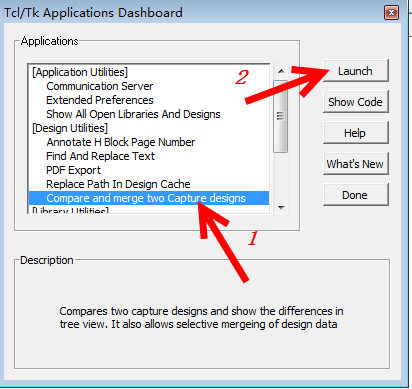

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

了35000多名硬创先锋报名参加线上线下培训会,并成功聚集了400多家生态合作伙伴,与 500多家顶级投资机构建立合作。过往八届赛事123家总决赛晋级企业中,有112家获得融资,融资金额突破167亿,获2轮及以上融资的企业占比达54%。02

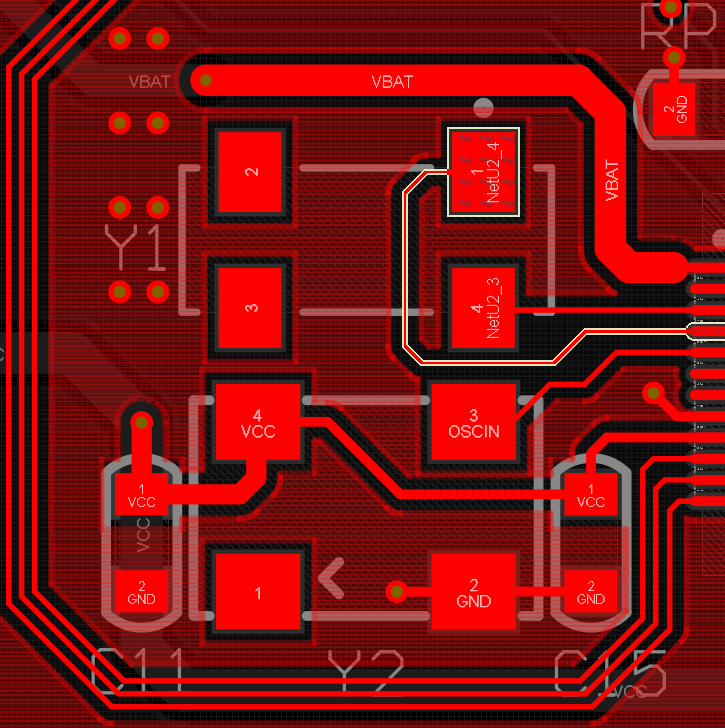

由于EDA软件众多,大家不可能对每个软件都是很熟悉的,这样如果有不同的原文件过来,我们要会转换成自己最熟悉的一种来进行。AD软件的PCB文件转换成PADS之后,颜色还是会跟AD中的显示一样,那怎样还更换显示的颜色呢,跟着视频来一探究竟。

元件封装

求助!!在绘制封装时,在3D界面按shift+鼠标拖动,为什么立体图形不会旋转,只显示action no aviable in3D view ?C:\Users\李行\Desktop\12345678

按照3D模型库添加库路径的方法添加完之后,打开PCB就提示错误。说steppath:variable not defined。需要进行怎么设置呢?C:\123.jpeg

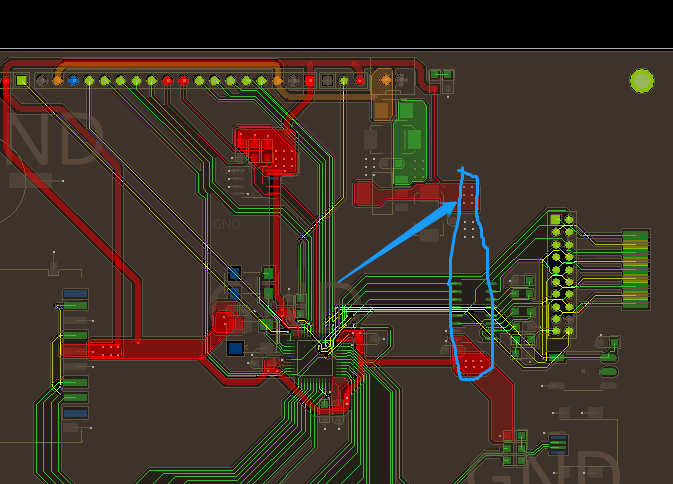

电源输出要从输出电容后面进行连接2.晶振需要包地处理,下面不要走别的信号线,包地需要打孔3.RS232 的升压电容走线需要加粗处理4.电源走线尽量加粗导20mil,满足载流5.USB尽量包地处理,并间隔100-150mil打上地过孔6.注意

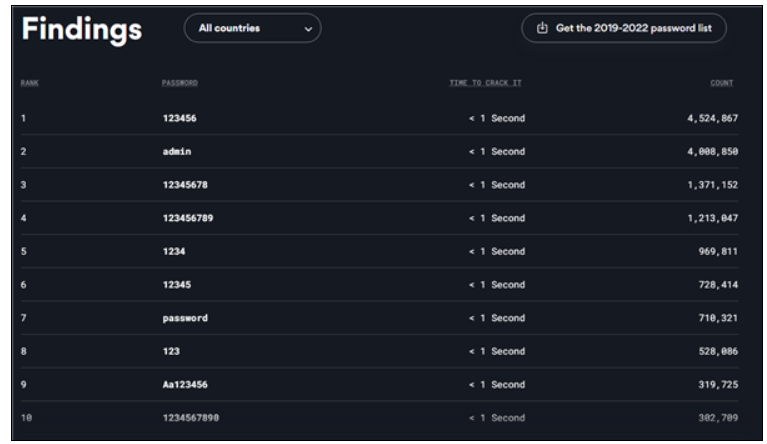

随着时代高速发展,密码逐渐成为了许多人的隐私保护手段之一,但有很多人设定的密码过于简单,很容易让人破解。最近,调研机构NordPass发布了2023年全球用户最长使用的200个密码,根据密码显示,其中123456以超过450万次数勇夺排行榜

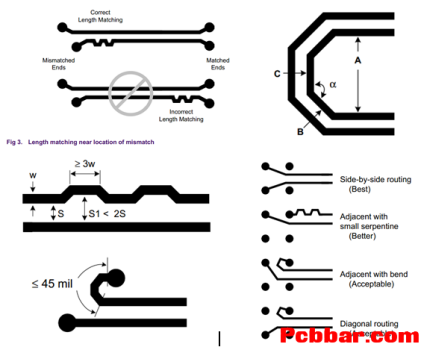

晶振需要包地,并且打上地过孔2.确认一下此处是否满足载流,自己加粗线宽3.差分包地需要在地线上打上地过孔4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.RS232尽量不要同层布线,如需同层建议间隔5W以上,不要走差分以上评审报

AP1236 是一款高精度,底噪声,CMOS LDO稳压器。AP1236提供底输出噪声,高波纹抑制率,底DROPOUT和非常快的开机时间,是当今前沿手机的理想选择。AP1236内部包括一个参考电原谅源,误差放大器,驱动晶体管,电流限制品和相

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

扫码关注

扫码关注