- 全部

- 默认排序

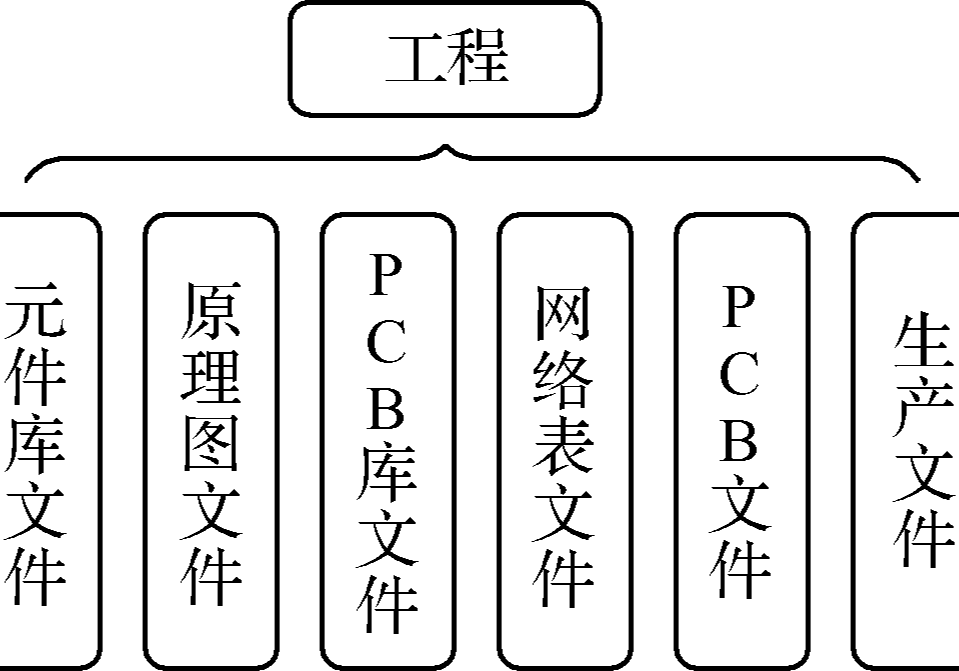

一个完整的PCB工程应该包含哪些内容?新一代Altium Designer集成了相当强大的开发管理环境,能够有效地对设计的各种文件进行分类及层次管理。本章通过图文的形式介绍工程的组成及完整工程的创建,有利于读者形成系统的文件管理概念。熟悉A

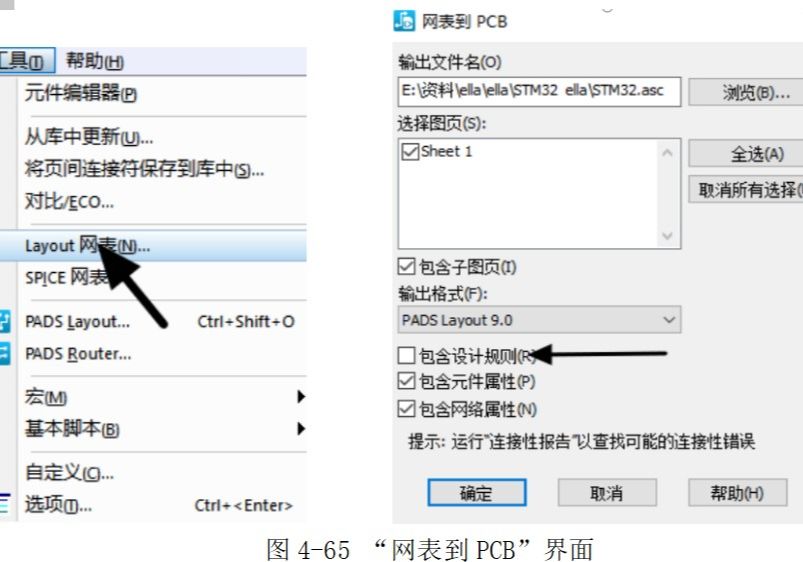

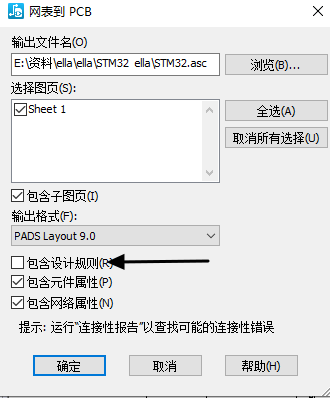

执行菜单命令“工具”→“Layout网表”进入到“网表到PCB对框,如图4-65所示。网表到PCB界面建议勾选“包含子图页”,“包含设计规则”项建议不勾选,其它的按照默认即可,“输出格式”栏选择合适的输出版本,“输出文件名”栏点击“浏览”按

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

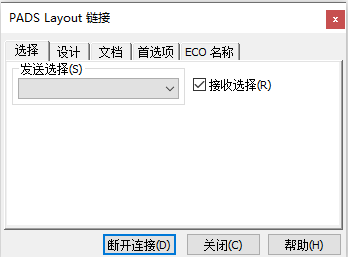

我们在画PCB时,经常会遇到要修改封装或修改原理图等操作。不推荐直接在PCB中非ECO模式下修改,这样会和orcad原理图不同步。我们采用修改orcad原理图,然后由pads layout软件来进行ECO网表的对比来修改我们的PCB文件。

我的是ad15,在做网络报表时只有如图四个选项卡,求高手指导(我装了ad19之后是有protel选项的,另外我ad14,15都试了,这两个版本都没有)

利用Altium Designer设计硬件电路时,如果需要硬件电路设计的印刷电路板比较简单,可以不参照硬件电路设计流程而直接设计印刷电路板,然后手动连接相应的导线,以完成设计。但对于复杂硬件电路设计时,可按照设计流程进行设计。1. 准备原理图与网络表

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注