1、耦合电容的放置,按照设计指南要求放置。如果没有设计指南时,若信号是IC到IC,耦合电容靠近接收端放置;若信号是IC到连接器,耦合电容请靠近连接器放置;

2、尽可能选择小的封装尺寸,减小阻抗不连续;

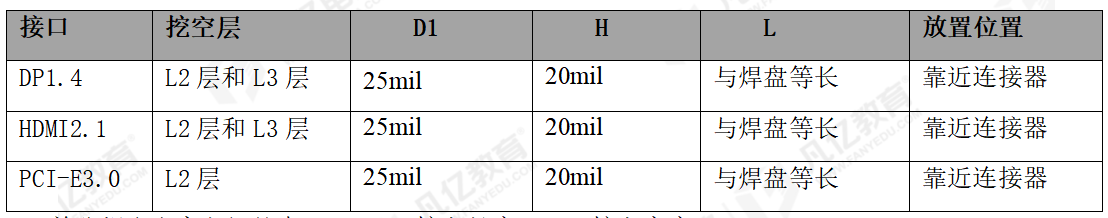

3、如果接口的信号工作速率≥8Gbps,那么这些接口的差分隔直电容建议按如下方式进行优化。

1)根据接口选择挖空一层或者两层地平面,如果挖空电容焊盘正下方L2地参考层,需要隔层参考,即L3 层要为地参考层;

2)如果挖空L2和L3地参考层,那么L4层要为地参考层。挖空尺寸需根据实际叠层通过仿真确定;以下给出基于EVB一阶HDI叠层的参考尺寸。

表1 耦合电容焊盘挖空尺寸参考值

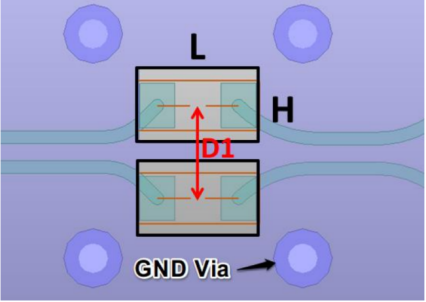

D1:差分耦合电容之间的中心距;L:挖空长度; H:挖空宽度。

4、在耦合电容四周打4个地通孔以将 L2~L4 层的地参考层连接起来,如图1所示。

图1 耦合电容的挖空与GND孔的放置

扫码关注

扫码关注