- 全部

- 默认排序

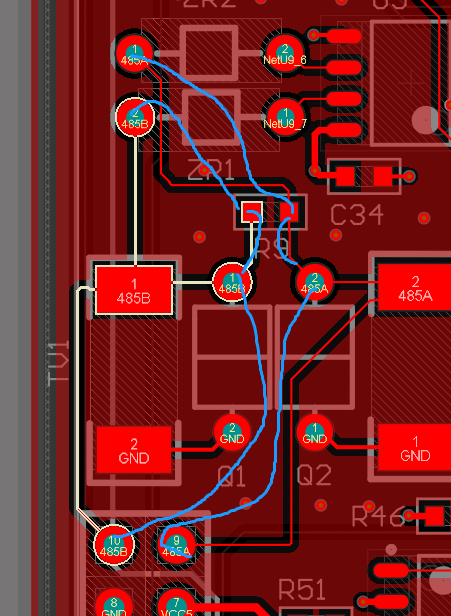

1.485需要走类差分处理或者加粗2.模拟信号需要一字型布局,走线需要加粗,并包地处理3.晶振需要走类差分处理晶振走线都需要优化一下4.差分走线需要按照阻抗线宽线距要求走,后期自己优化一下5.注意地分割,模拟地不要进去数字地里面,分割间距1

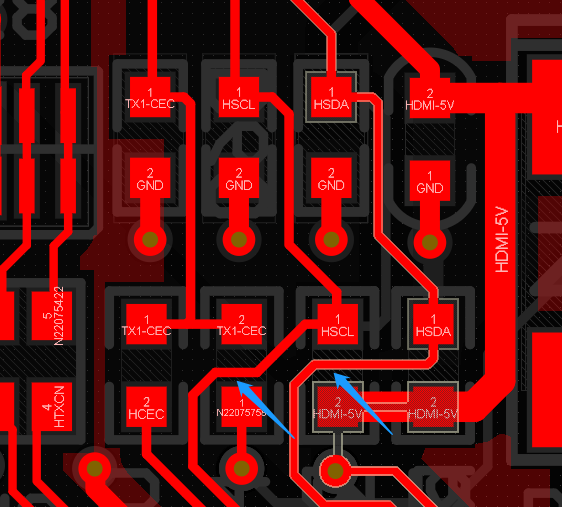

网口除差分信号外,其他信号都需要加粗到20mil2.注意网口的地分割,跨接器件旁要多打地过孔,分割间距2mm后期自己处理一下3.差分出线需要优化一下,器件可以摆放远一点,包地的线要需要均匀打上过孔4.注意差分信号需要按照阻抗线距进行走线晶振

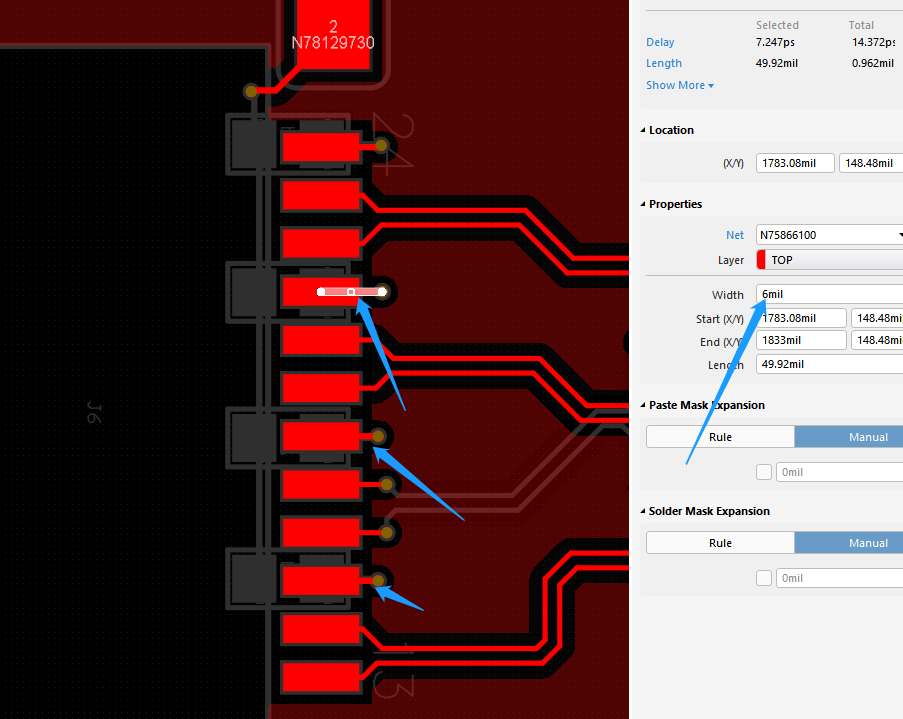

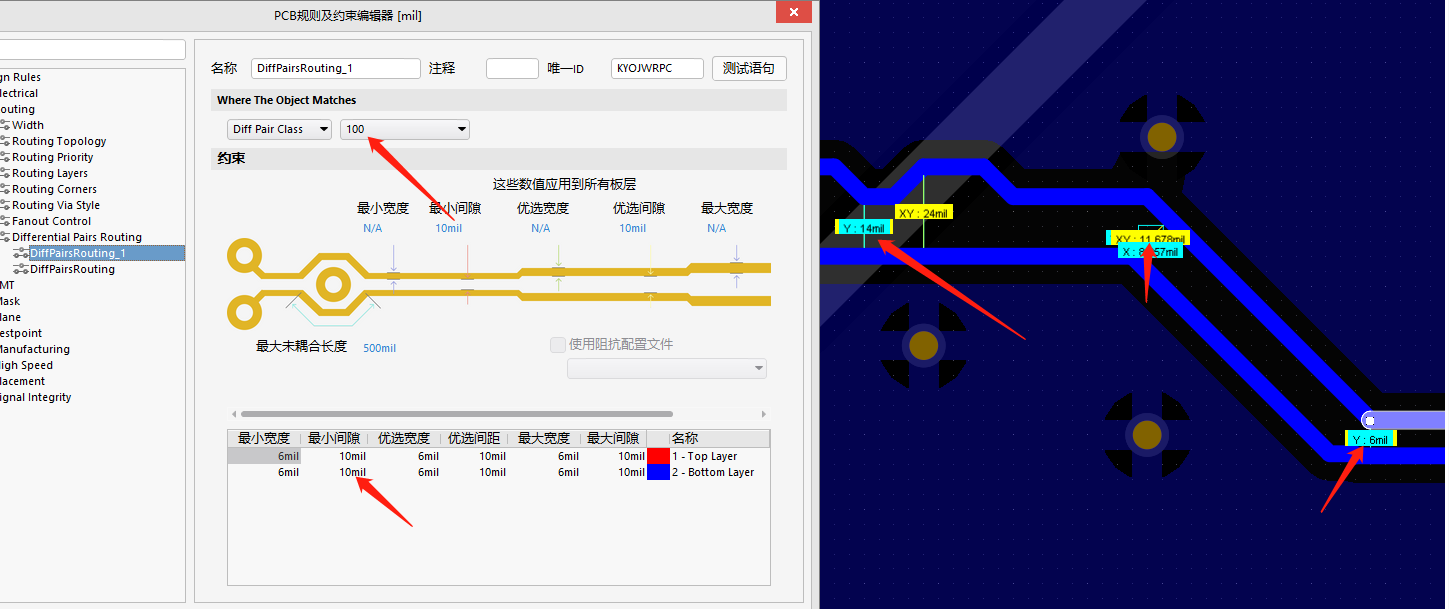

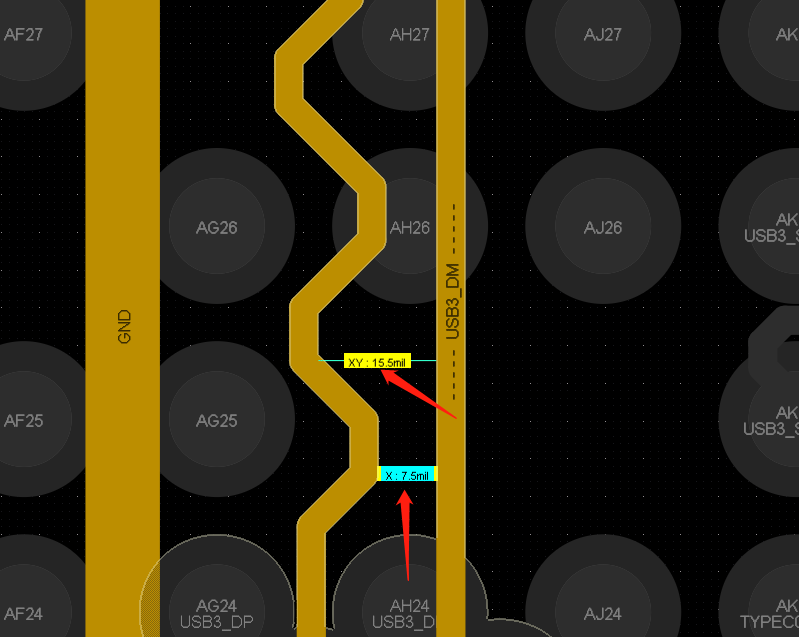

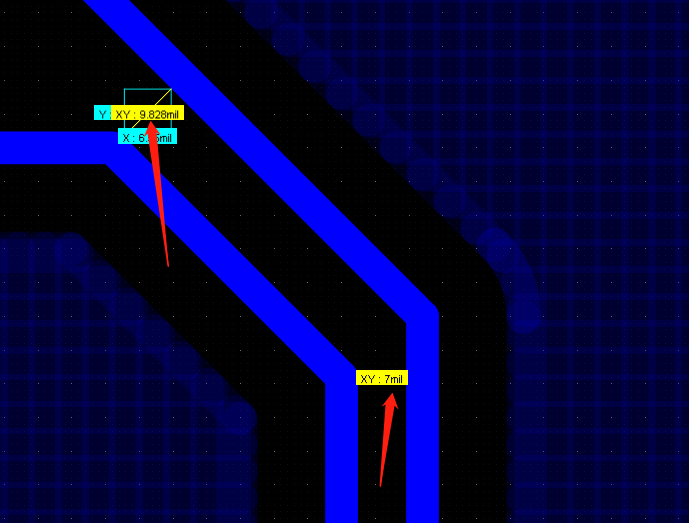

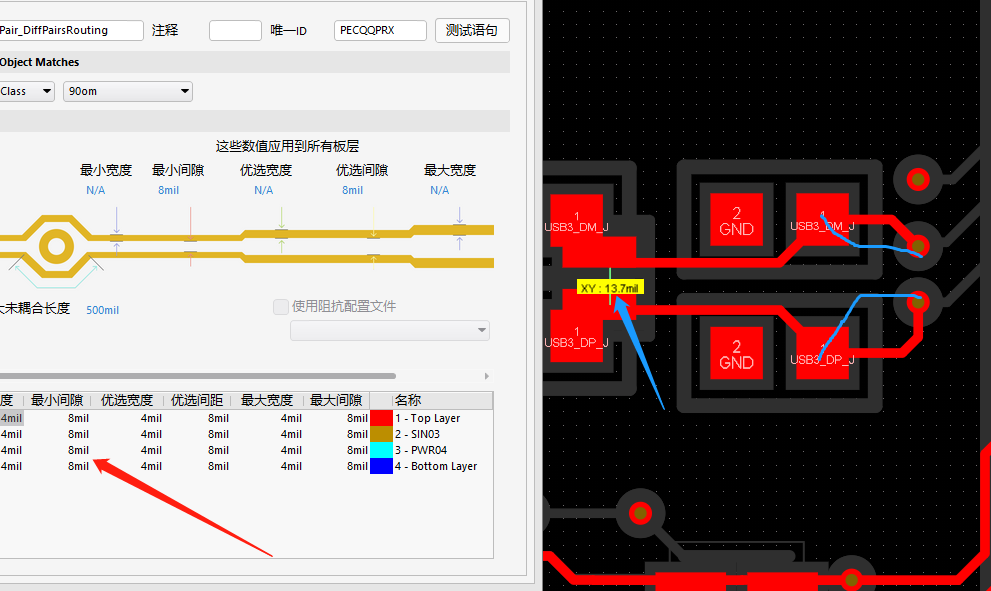

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

注意差分出线要尽量耦合,走一起2.注意差分走线需要按照阻抗线宽线距走线,否则容易产生阻抗突变3.打孔要打在ESD器件前面4.走线一层连通不用打孔差分需要进行对内等长,误差5mil差分对内等长凸起高度不能超过线距的两倍注意器件摆放不要干涉一脚

差分对内等长凸起高度不能超过线距的两倍2.焊盘出线可以在优化一下3.差分走线需要按照阻抗线宽线距进行走线4.pcb上不要存在stub线5.注意差分对内等长误差5mil6.存在多处开路,后期自己检查一下drc7.过孔到焊盘间距太近,间距最少6

差分需要按照阻抗线距走,后期埃及调整一下2.差分对内等长凸起高度不能超过线距的两倍网口座子需要靠近板框摆放3.差分出线要尽量耦合,走线需要优化一下4.时钟信号包地需要在地线上打孔,建议50mil-100mil一个以上评审报告来源于凡亿教育9

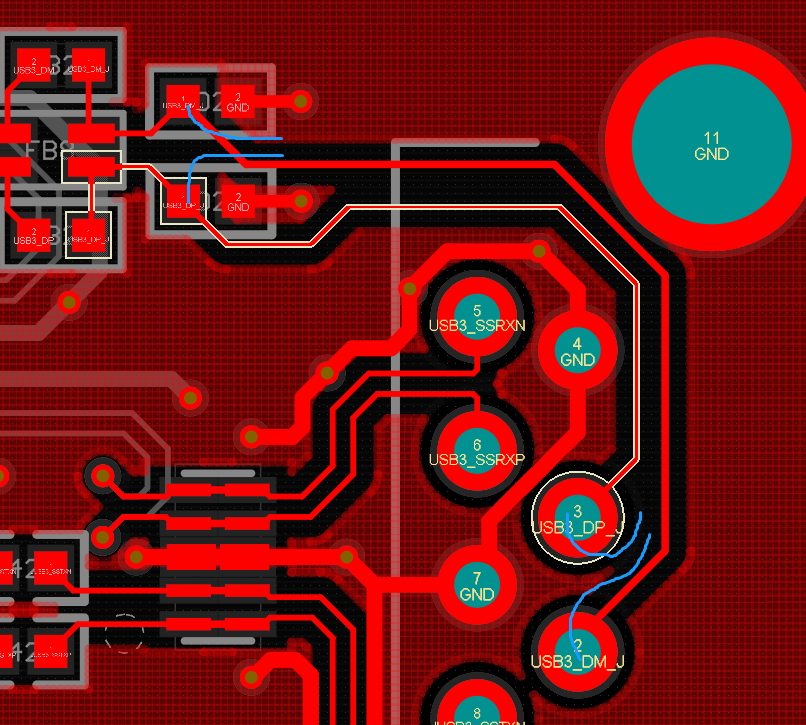

差分走线要按照阻抗间距走,差分出线要尽量耦合,后期自己优化一下有好几处差分没有按照阻抗线距走,后期自己调整一下2.差分对内等长凸起高度不能超过线距的两倍3.CC1和CC2属于重要信号,走线需要加粗4.走线需要优化一下,尽量不要有直角5.差分

走线尽量不要从器件中心穿,间距太近,后期容易造成短路2.USB 5V供电,电容先大后小摆放3.数据线之间等长需要满足3W间距4.注意过孔不要上焊盘,差分出线要尽量耦合5.差分走线不满足阻抗线宽,对内等长凸起高度不能超过线距的两倍6.WIFI

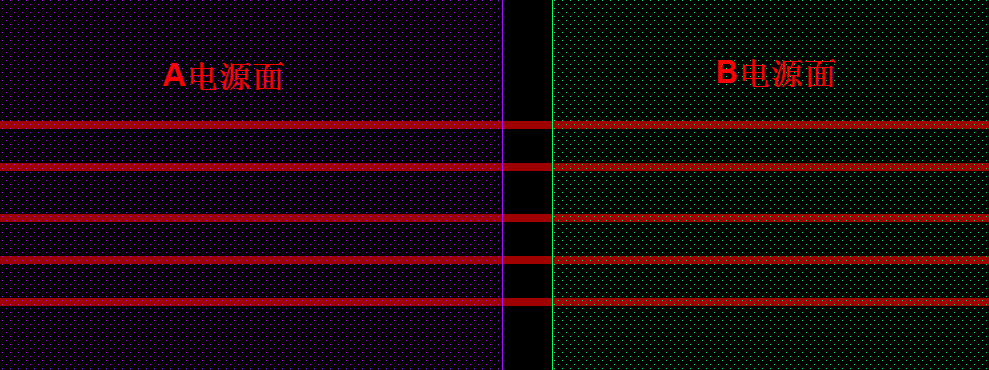

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

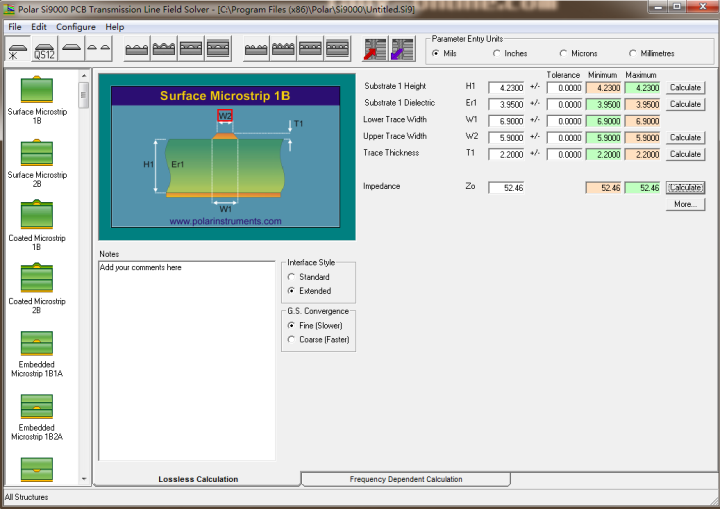

答:特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。

全站最新内容推荐

- 1AD-全能20期-SMT32-两层板-20期-杨文越

- 290天全能特训班22期-莱布尼兹的手稿 第十九次作业 SDRAM

- 3飞龙套餐Altium Designer篇(PCB、硬件、EMC、单片机)

- 4飞龙套餐PADS篇(PCB、硬件、EMC、单片机)

- 5飞龙套餐allegro篇(PCB、硬件、EMC、单片机)

- 6AD-全能21期-DM642开发板第一次作业

- 72024年中国及31省市3D打印市场分析及国家政策汇总

- 8AD- 杨皓文 第七次作业 2片SDRAM设计(菊花链)

- 990天全能特训班22期AD-沸点-2SDRAM

- 102.4GHz/6GHz Wi-Fi 带通滤波器: ACPF-7A24-TR1、ACPF-W065-TR1 产品介绍、特征及应用

扫码关注

扫码关注