- 全部

- 默认排序

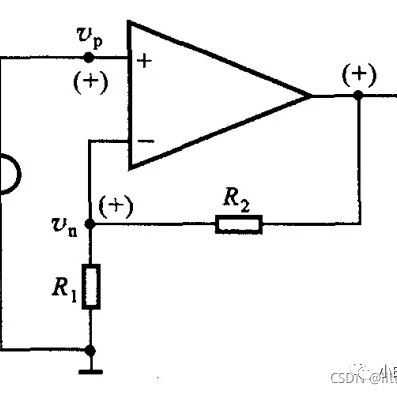

模电我想从运放开始讲起。首先是运放的基本特性、基本电路,到复杂一些的电路,最后讲讲实际工程设计时,需要关注运放的哪些特性。本系列的文章都是从理论出发,结合实际例子,最终落实到工程应用中。一、运放的基本特性运放的两个输入端的电流可以近似为0,即图中的ip和iN都为0。运放的输出取决于两个输入端电压的

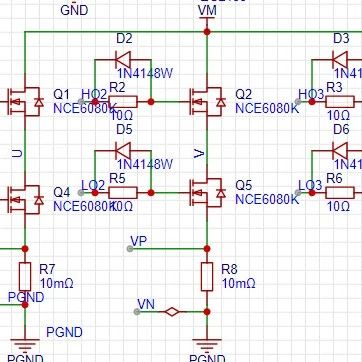

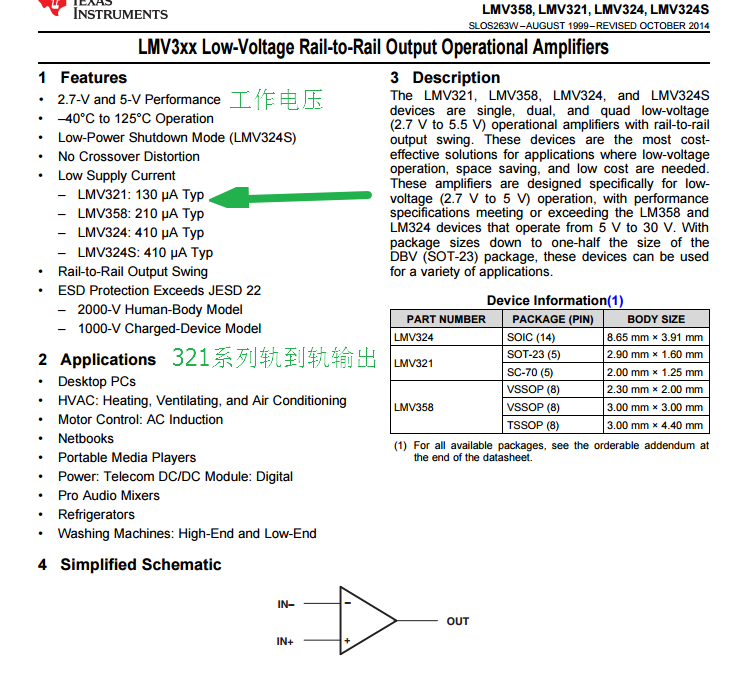

FOC中必不可少的一环就是电流采样,而直接对电流进行采样难度较大,使用采样电阻将电流信号转化为电压信号再对电压进行进行采集处理,就可以得到电流的数值,所以涉及到采样电阻的选择与ADC的使用。图1 运放搭建运放使用lmv358芯片,对两相电流进行采样,对U与W相电流进行采样。图2 采样原理图这里对UW

集成运算放大器,也就是我们常说的运放,在日常生活中极为常见,也是电子工程师需要重点学习如何使用的电子元器件之一,今天本文将分享介绍集成运算放大器,希望对小伙伴们有所帮助。1、集成电路①分立元件电路:由互相分开的晶体管、电阻、电容等电子元器件

模拟电路电路设计的九个阶段,类似下围棋的段位。从一段到九段都看完后,就掌握自身是哪一个时期的水平了。不容错过哦。 一开始步入这一行,对PMOS/NMOS/BJT那些的只不过是有一个大概的掌握,各类元器件的性能都不太清晰,实际电路设计成哪样的电路也没有想法,路原理图主要是看国内杂志期刊上的文章,或是依照教材上现成的电路,总感觉他们说得都是有道理。做的电路主要是是小规模的模块,做些差分运放,或是带隙基准的仿真那些的就计算着发文章,生怕到时候论文凑不够。总的来说,基本上看见运放还是发怵。感觉spic

运放电流检测电路

使用运放电流检测,检测方式有高端检测和低端检测两种运放电路。高端运放电流检测优点:-可以检测区分负载是否短路-无地电平干扰缺点:-共模电压高,使用非专用分立器件设计较复杂、成本高、面积大低端运放电流检测优点:-共模电压低,可以使用低成本的普通运算放大器缺点:-检流电阻引入地电平干扰,电流越大地电位干扰越明显

前言反相运算放大电路是一种常见的基本运算放大电路。反相运算放大电路设运算放大器的输入阻抗无穷大,也就是说在运算放大器的反相输入端“-”无电流流入或流出,根据运算放大器的“虚短”,运放正相输入端“+”和反相输入端“-”电压相同,因此反相输入端

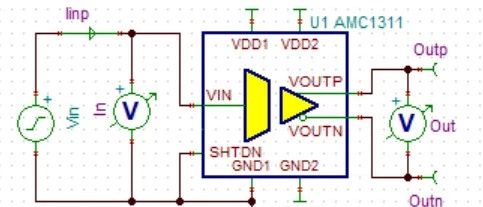

隔离运放在电机驱动中的应用电机驱动器是用来控制各种电机,比如AC变频器,伺服电机的一种控制器。一般是通过位置、速度和力矩三种方式对电机进行控制,实现传动系统定位。高分辨率、精确电压电流测量在需要高性能扭矩和运动控制的工业电机驱动应用中至关重要。因为工业电机驱动器需要满足 (IEC) 61800-5-

电子设计中电容的选择

在电子设计芯片的电源输入端一般都会加一颗贴片电容,比如单片机的电源输入端、运放的电源输入端等,电容的个数与电源的通道数一致。一般这个电容选用0.1uF的。如下图所示是AT24C02电源引脚所接的电容。 单片机或者是通信芯片等需要用到晶振的芯片,在设计无源晶振电路时,用两个电容和晶振构成震荡起振电路为芯片提供时钟频率。一般这个电容的选择范围为(15-30)pF,有的芯片会在数据手册上写明不同晶振下该选用多大的电容。 电容具有储能作用,通过设计不同的串联电阻,可以改变电容的充放电速度,也就起到了

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注