- 全部

- 默认排序

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

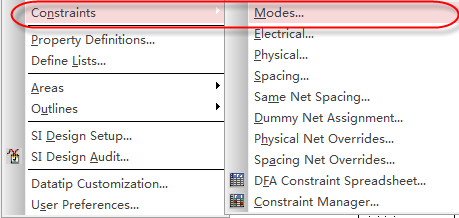

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

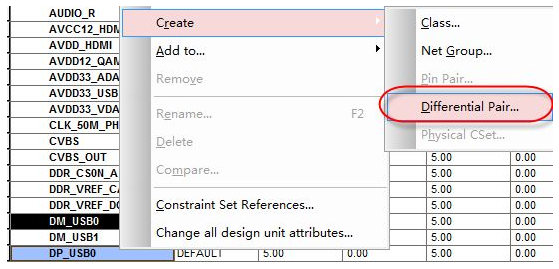

设计PCB过程中,若设计中有差分对信号,则需要将是差分的2个信号设置为差分对,设置差分对有2种方式:手动添加及自动添加一、手动添加差分对:1、点击Setup-Constraints-Constraint Manager调出CM规则管理器,然

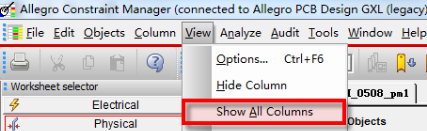

答:正常情况下CM规则管理器中属性较多,有很多列,如果有部分列我们不想显示,则可以隐藏,具体操作的步骤如下所示:第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器。然后找到想隐藏的属性列(如Max Length),然后右击点击Hide Column选项,如图5-196所示,即可隐藏此列内容;

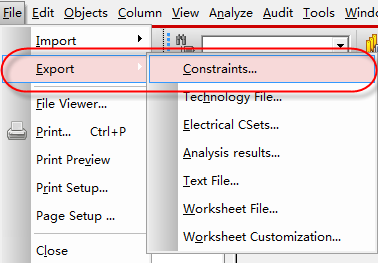

答:我们使用Allegro软件进行PCB设计,其中的PCB布局布线都可以进行复用,那么它所设置的规则,比如物理规则、间距规则,是否也可以进行复用呢,当然是可以的,具体复用操作的步骤如下所示:第一步,打开已经设置好规则的PCB文件,执行菜单命令Setup-Constraints,在其下拉菜单中选择Constraint Manager,进入到规则管理器中;

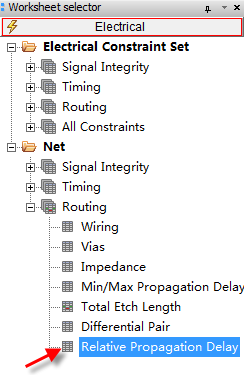

答:在第5.35问中,我们讲述了直接添加的办法去添加相对传输延迟的等长规则。这一问呢,我们讲述一下如何使用模型添加法去添加相对传输延迟的等长规则,具体的操作步骤如下所示:第一步,打开规则管理器,执行菜单命令Setup-Constraints,在下拉菜单中选择Constraint Manager,如图5-99所示,进入到规则管理器中;

大神们好! 看了郑总的2层板视频,根据视频设置了走线规则和过孔规则后在走线或防止过孔时发现尺寸和设置的规则不一致。具体情况如下:过孔 规则设置过孔是10-18mil,放置时使用快捷键P+V或者点击工具栏放置的过孔为28-50mil,而在走线状态下按下“*”键防止的过孔是和规则一致的,如下图:问

扫码关注

扫码关注