- 全部

- 默认排序

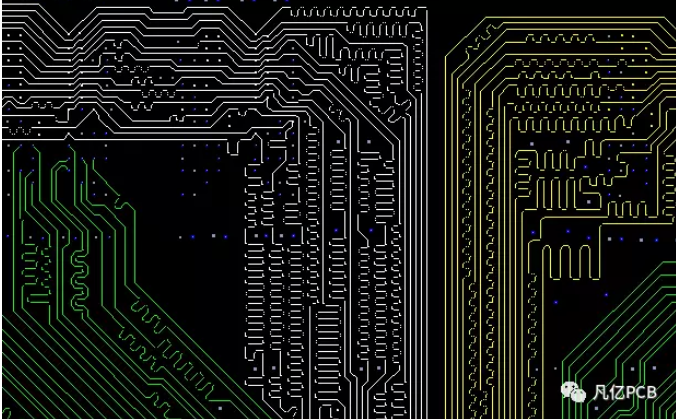

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的 PCB 信号等长处理。等长的目标

蛇形走线是PCB布局布线中常用的特殊走线之一,也是小白初入PCB设计中的难点之一,今天将以蛇形走线为主,重点分享它的技巧和用法,希望对小伙伴们有所帮助。蛇形走线外文名为serpentine,是PCB布局布线的一种特殊走线方式,主要目的是为了

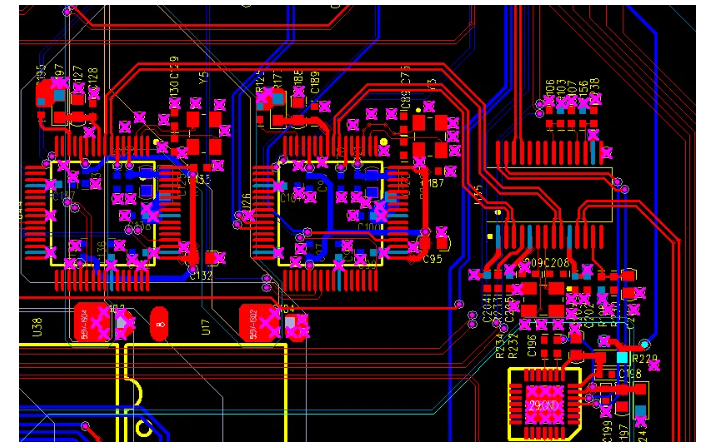

PADS蛇形等长处理

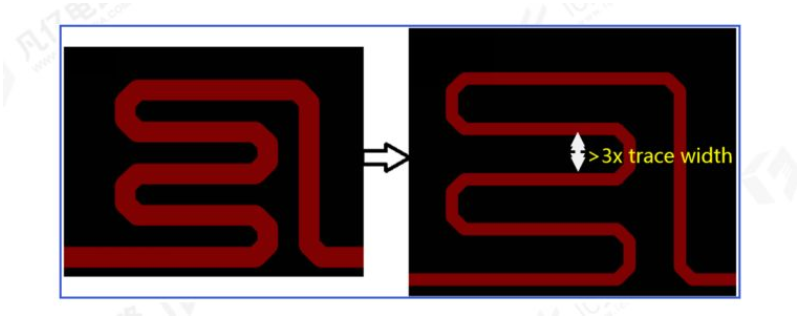

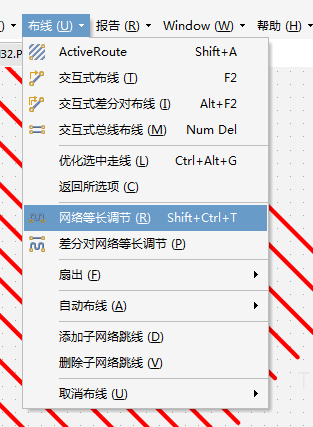

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

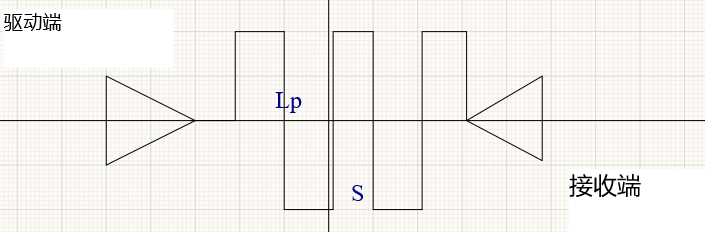

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

PCB设计信号等长分析

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

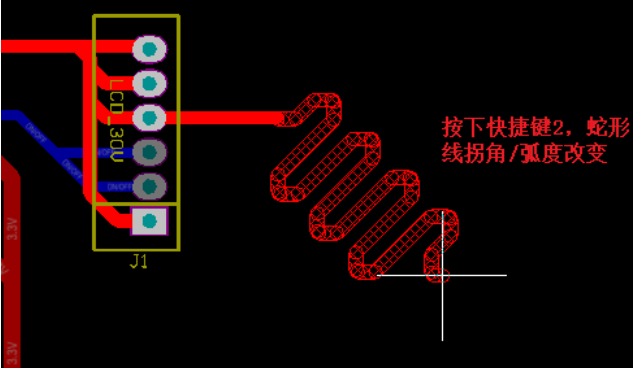

PCB设计,遇到差分线,需要做等长设计时,该怎么操作呢?在做走线等长设计的时候,我一般都是采用让走线进入蛇形走线模式,然后走出蛇形线来快速完成等长设计。

扫码关注

扫码关注