- 全部

- 默认排序

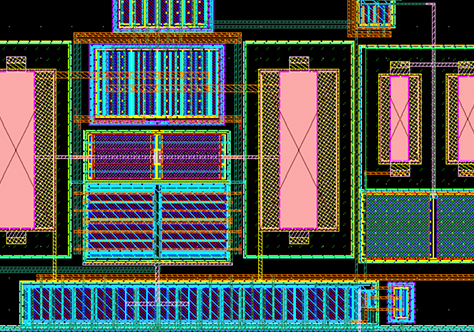

目前,IC设计产业已成为半导体行业金字塔的顶端,IC设计工程师岗位也自然成为首选热门高薪岗位之一,越来越多的人来选择IC设计发展,为帮助小伙伴们在IC设计道路上走得更顺,今天我们来聊聊IC设计中的互连线随着技术发展,集成电路CD的不断缩小,

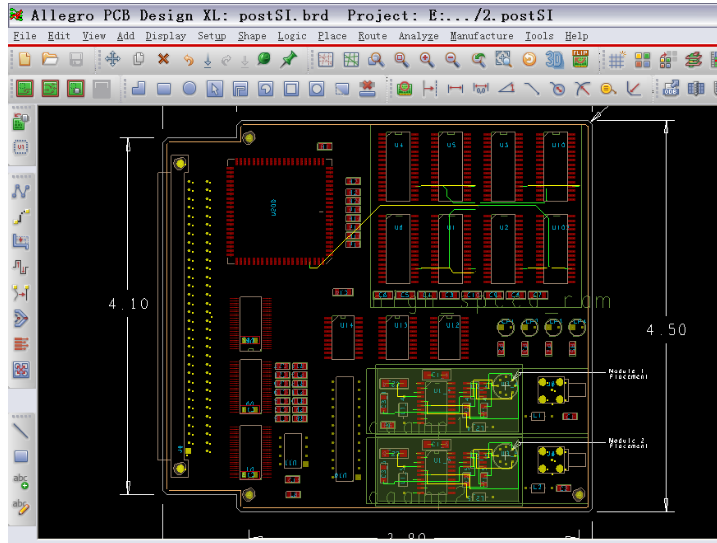

1.菜单栏(1)File(文件):主要用于完成对各种文件的新建、打开、保存等操作。(2)Edit(编辑):用于完成各种编辑操作,包括撤销、取消、复制及粘贴。(3)View(查看):用于视图操作,包括窗口的放大、缩小,工具栏的打开、关闭及网格

世界著名社会学家乔恩·范·戴克对使用“数字鸿沟”一词持谨慎态度,因为它太过模糊。这个术语反复强调,存在两个独立的因素:高技术获取和低技术获取,然而,问题远不止于此。影响技术鸿沟的因素有很多,包括政治、自由、资本、资源、参与、能力、教育和技能

常用VIEW视图快捷命令:命令快捷键功能说明适合文件VD当设计图页不在设计目视范围内,可快速归位适合所有对象VF对整个图纸文档进行归位放大Page up以鼠标指针为中心进行放大缩小Page down以鼠标指针为中心进行缩小选中的对象VE可以

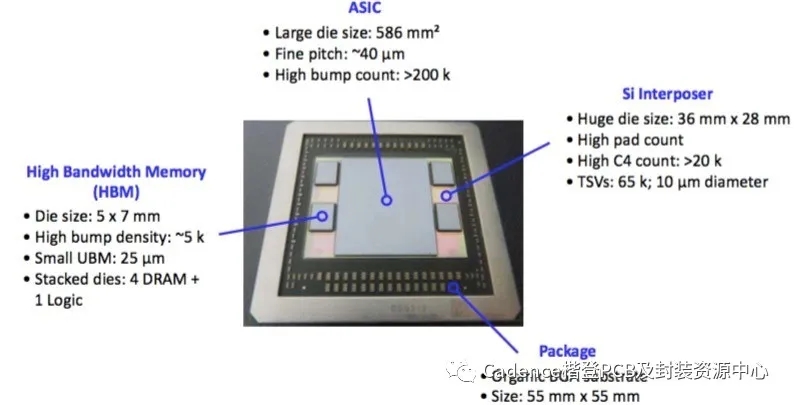

50多年来,半导体行业一直受益于摩尔定律。但是如今,半导体等比例缩小的时代已经结束。摩尔定律主要是作为一条经济法而存在——即集成电路上可容纳的晶体管数量,约每隔几年便会增加一倍。当然,是技术的发展使之成为现实;直到几年前,这一定律依然适用。高层次的经济主张是:每一代工艺将同一领域的晶体管数量增加一倍,成本仅增加15%,从而为每个晶体管节省35%的成本。但是因为当今的工艺愈发复杂,加之建造一个工厂的资本投入非常大(每台EUV步进机将耗资1亿美元),导致每一代晶体管都更加昂贵。因此我们发展出一个从7

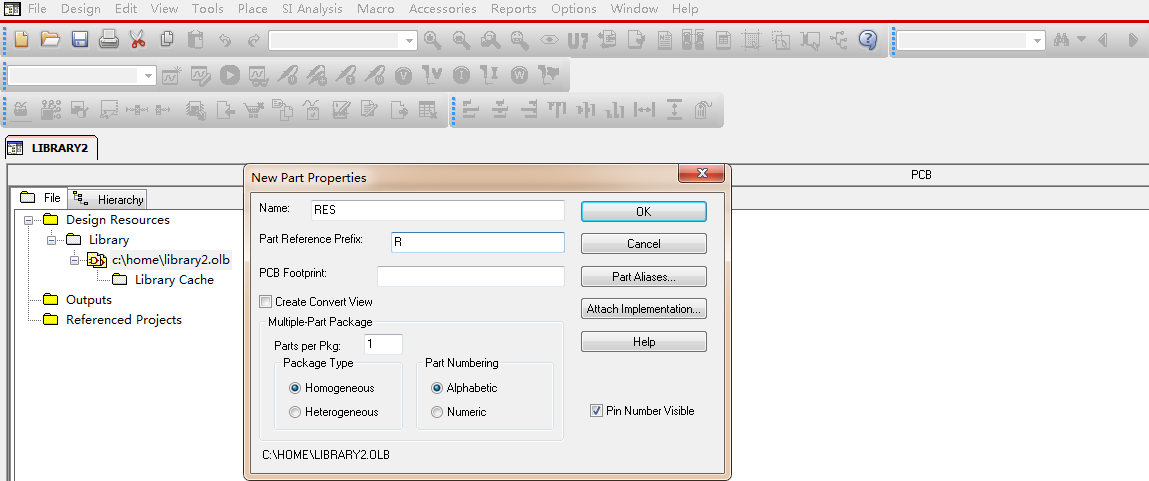

我们以一个电阻的封装为例,详细讲解创建一个简单分立元器件步骤:第一步,按照我们前面的问答中详细介绍,新建一个库文件,如图2-11所示,填写名称为RES,起始名称为R,PCB封装那一栏先可以不用填写,分立器件,Part选择1即可,其它按照默认设置; 图2-11 新建RES的库文件是示意图第二步,在弹出的R?的虚线框,在右侧栏选择Place Rectangle,绘制一个合适的矩形框在虚线内部,运用菜单栏上的Snap To Grid,关掉格点,将矩形框调整到合适的位置,然后将虚线框缩小至跟矩

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

扫码关注

扫码关注