- 全部

- 默认排序

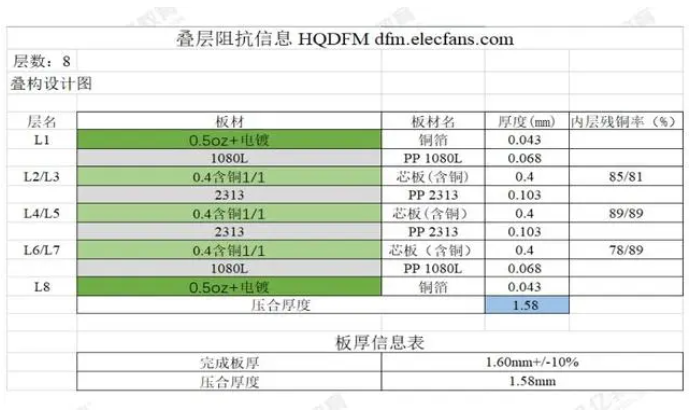

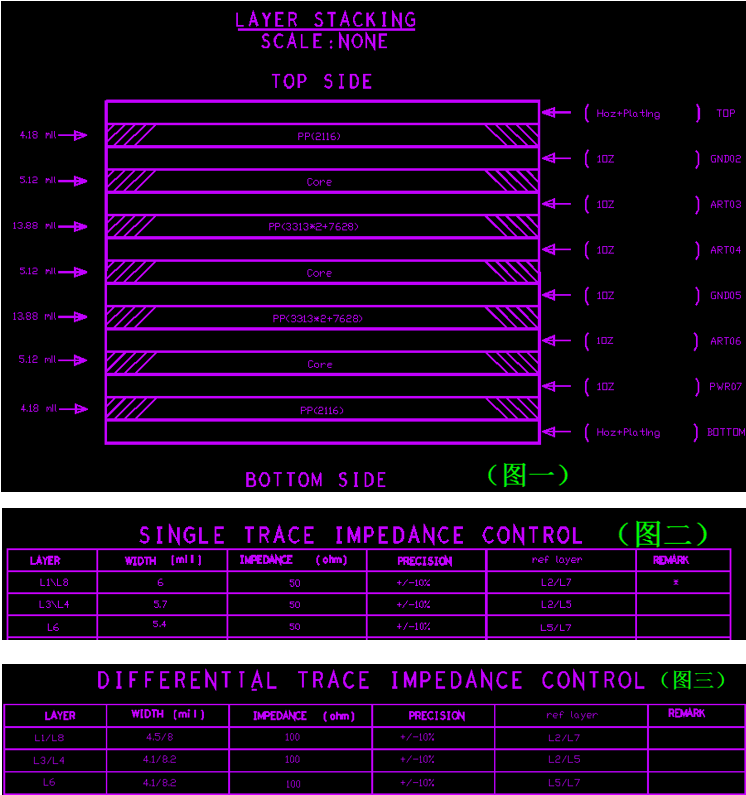

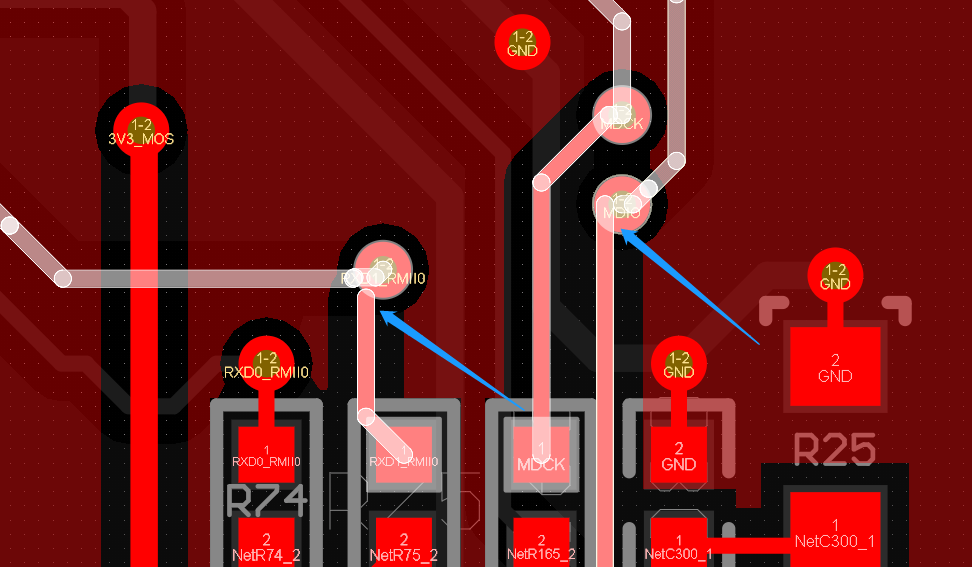

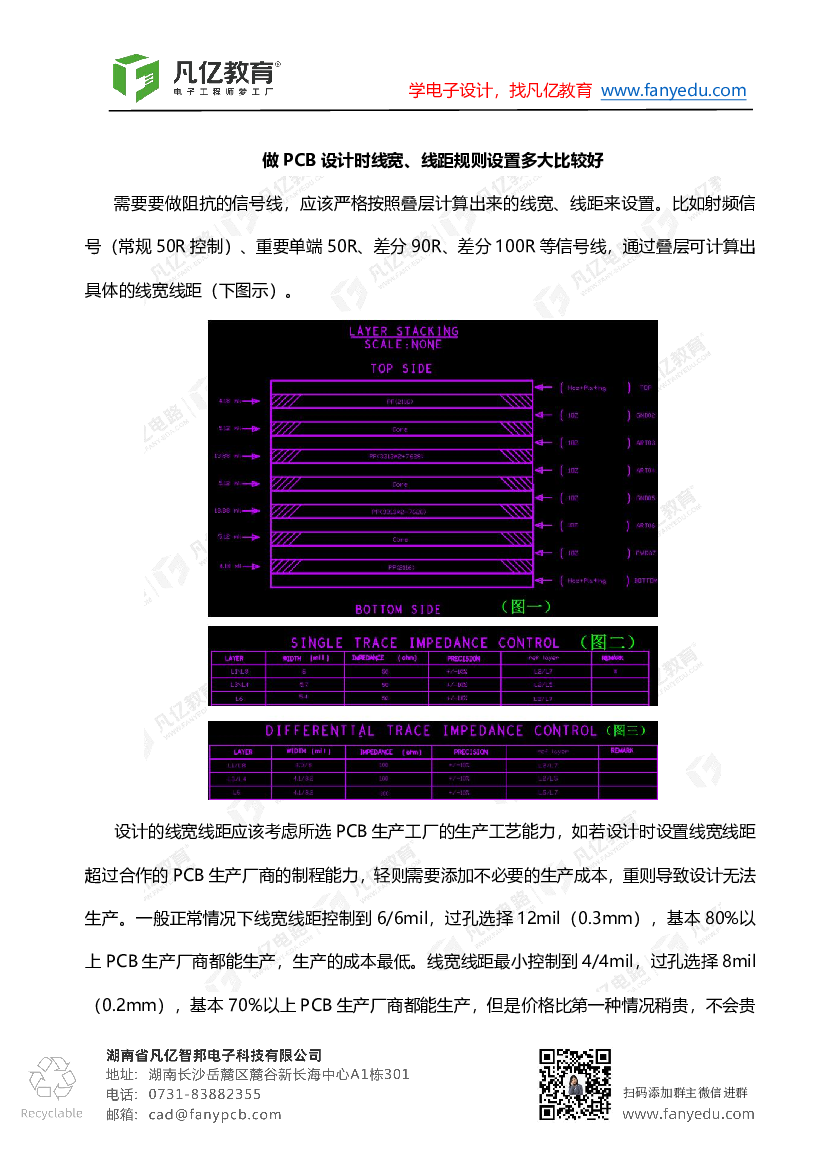

为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。由于最小线宽和最小线

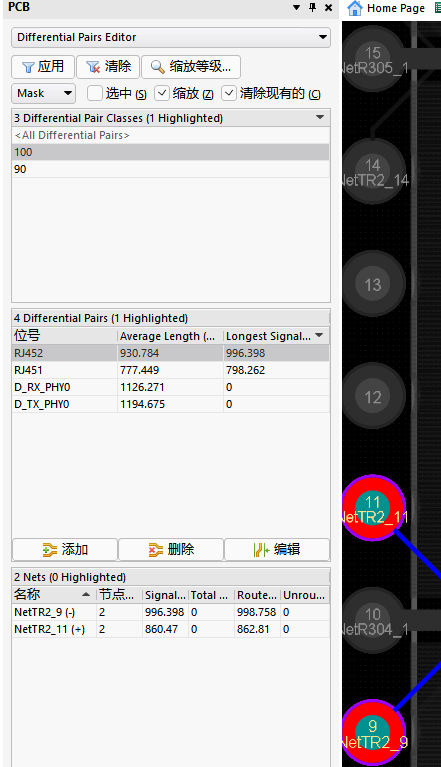

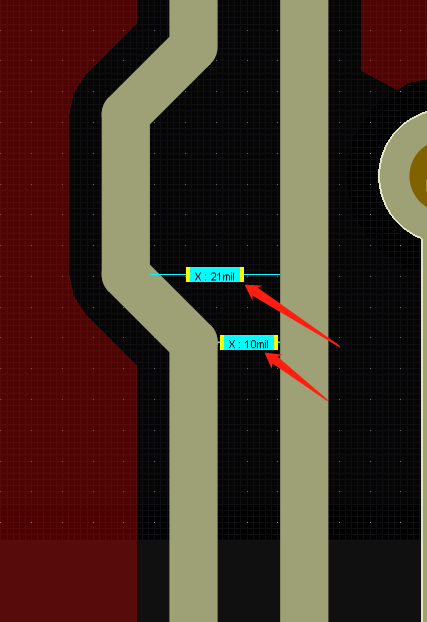

网口的差分信号需要对内等长,误差5mil2.差分出线要尽量耦合3.走线未连接到过孔中心4.RJ45座子需要挖空5.pcb上存在短路6.差分走线不满足差分规则7.锯齿状等长不能超过线距的两倍8.出线宽度超焊盘宽度,与焊盘同宽即可9.时钟包地需

差分锯齿状等长不鞥超过线距的两倍2.差分换层打孔尽量在旁边打上一对回流地过孔3.232的升压电容尽量走线加粗到15mil4.注意晶振需要包地处理,并在地线上打上地过孔5.注意满足载流大小6.USB差分对内等长误差5mil以上评审报告来源于凡

走线未连接到过孔中心2.差分出线需要优化一下3.线宽突变,确认一下具体线宽,尽量保持统一4.电源一层连通,无需打孔5.差分处理不规范,锯齿状等长不能超过线距的两倍6.pcb上存在开路7.RJ45座子需要挖空以上评审报告来源于凡亿教育90天高

我有块板子,ETH_TX_P/TX_N/RX_P/RX_N,芯片与网口(HR11105A),布线距离是 4300mil,网口灯一闪一闪的连上就断开,是不是布线过长了?」

扫码关注

扫码关注