为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

层的定义设计原则:

1)主芯片相临层为地平面,提供器件面布线参考平面;

2)所有信号层尽可能与地平面相邻;

3)尽量避免两信号层直接相邻;

4)主电源尽可能与其对应地相邻;

5)原则上应该采用对称结构设计。对称的含义包括:介质层厚度及种类、铜箔厚度、图形分布类型(大铜箔层、线路层)的对称。

PCB的层定义推荐方案:具体的PCB层设置时,要对以上原则进行灵活掌握,根据实际的需求,确定层的排布,切忌生搬硬套。以下给出常见的层排布推荐方案,供参考。在层设置时,若有相邻布线层,可通过增大相邻布线层的间距,来降低层间串扰。对于跨分割的情况,确保关键信号必须有相对完整的参考地平面或提供必要的桥接措施。

RK3588目前使用10层1阶, 10层2阶, 8层通孔等PCB叠层,以下叠层结构做为范例,可以给客户在叠层结构的选择和评估上提供帮助。如果选择其他类型的叠层结构,请根据PCB厂商给出的规格,重新计算阻抗。

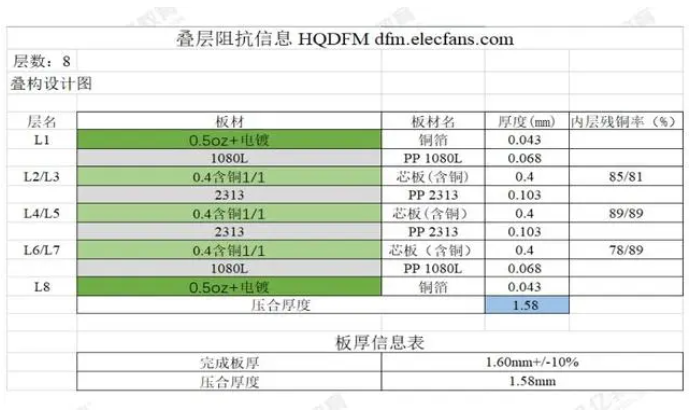

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.6mm,详细的叠层设计如表1-1所示。

表1-1 8层通孔板1.6mm厚度叠层设计

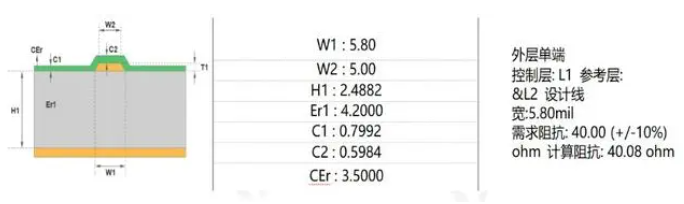

①外层单端40欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为5.8mil,L1与L8层是对称设计,故L1层与L8层40欧姆单端走线为5.8mil。如图1-1所示。

图1-1 外层单端40欧姆走线阻抗设计

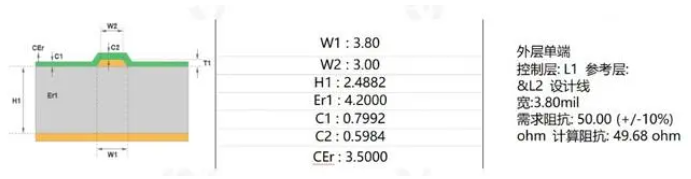

②外层单端50欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为3.8mil,L1与L8层是对称设计,故L1层与L8层50欧姆单端走线为3.8mil。如图1-2所示。

图1-2 外层单端50欧姆走线阻抗设计

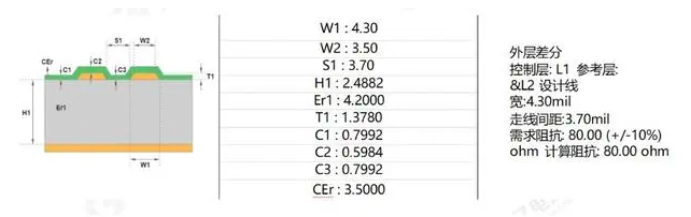

③外层差分80欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为4.3/3.7mil,L1与L8层是对称设计,故L1层与L8层80欧姆差分走线为4.3/3.7mil。如图1-3所示。

图1-3 外层差分80欧姆走线阻抗设计

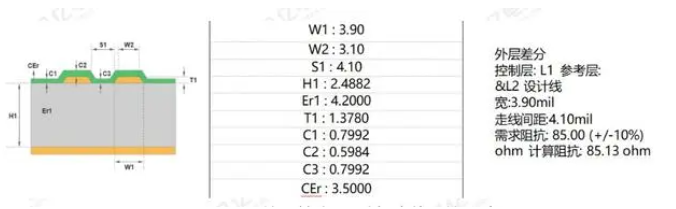

④外层差分85欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.9/4.1mil,L1与L8层是对称设计,故L1层与L8层85欧姆差分走线为3.9/4.1mil。如图1-4所示。

图1-4 外层差分85欧姆走线阻抗设计

⑤外层差分90欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.6/4.4mil,L1与L8层是对称设计,故L1层与L8层90欧姆差分走线为3.6/4.4mil。如图1-5所示。

图1-5 外层差分90欧姆走线阻抗设计

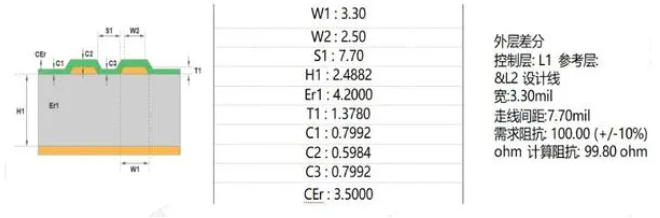

⑥外层差分100欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.3/7.7mil,L1与L8层是对称设计,故L1层与L8层100欧姆差分走线为3.3/7.7mil。如图1-6所示。

图1-6 外层差分100欧姆走线阻抗设计

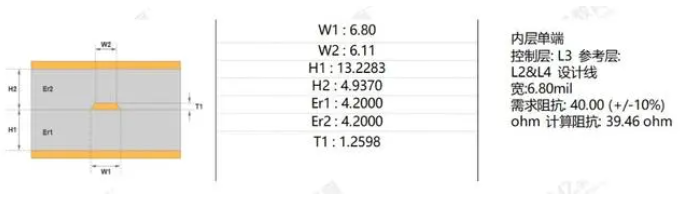

⑦内层单端40欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为6.8mil,L3与L6层是对称设计,故L3层与L6层40欧姆单端走线为6.8mil。如图1-7所示。

图1-7 内层单端40欧姆走线阻抗设计

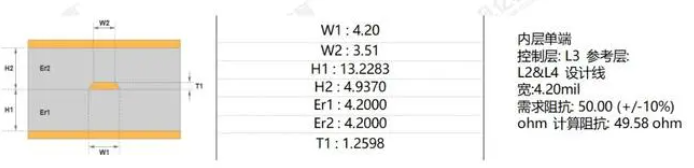

⑧内层单端50欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为4.2mil,L3与L6层是对称设计,故L3层与L6层50欧姆单端走线为4.2mil。如图1-8所示。

图1-8 内层单端50欧姆走线阻抗设计

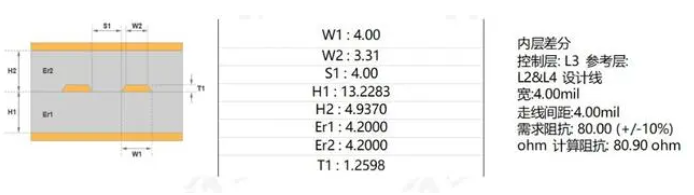

⑨内层差分80欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为4.0/4.0mil,L3与L6层是对称设计,故L3层与L6层80欧姆差分走线为4.0/4.0mil。如图1-9所示。

图1-9 内层差分80欧姆走线阻抗设计

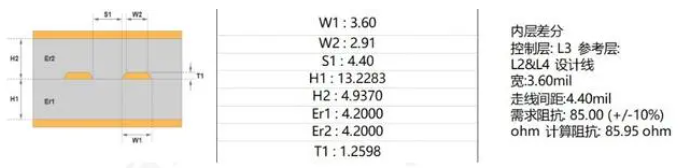

⑩内层差分85欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.6/4.4mil,L3与L6层是对称设计,故L3层与L6层85欧姆差分走线为3.6/4.4mil。如图1-10所示。

图1-10 内层差分85欧姆走线阻抗设计

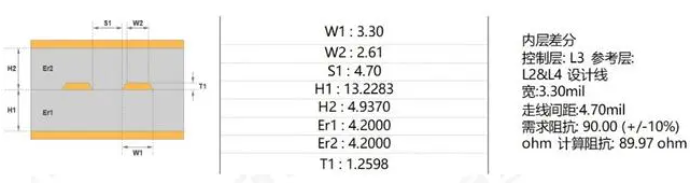

⑪内层差分90欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.3/4.7mil,L3与L6层是对称设计,故L3层与L6层90欧姆差分走线为3.3/4.7mil。如图1-11所示。

图1-11 内层差分90欧姆走线阻抗设计

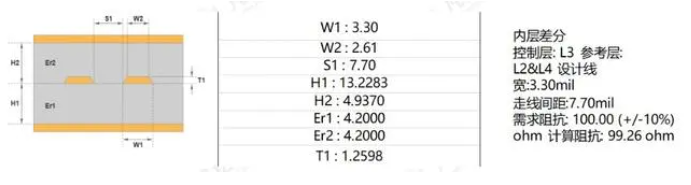

⑫内层差分100欧姆阻抗设计:使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.3/7.7mil,L3与L6层是对称设计,故L3层与L6层100欧姆差分走线为3.3/7.7mil。如图1-12所示。

图1-12 内层差分100欧姆走线阻抗设计

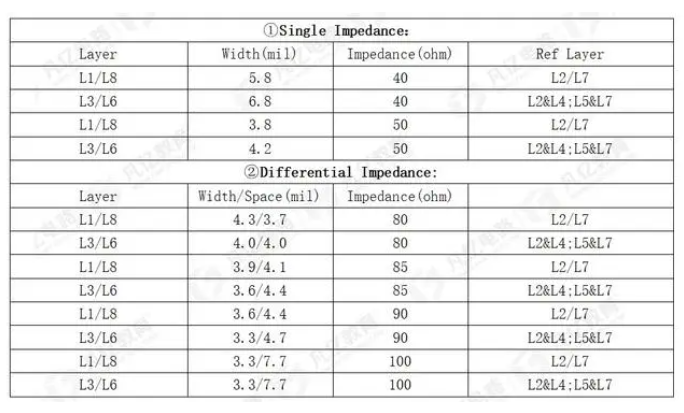

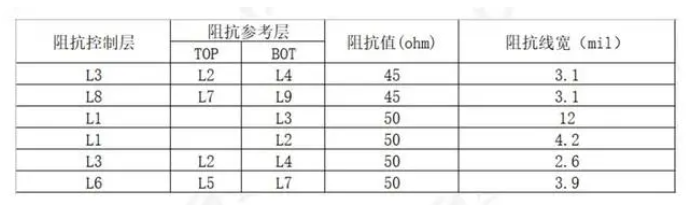

总体阻抗走线线宽如下表1-2所示:

表1-2 8层1.6mm总体阻抗走线线宽

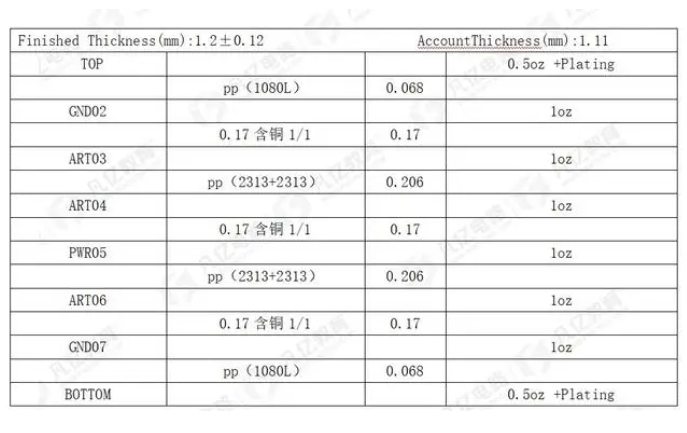

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.2mm,详细的叠层设计如表1-3所示。

表1-3 8层通孔板1.2mm厚度叠层设计

按照图1-3所示叠层设计参数,使用华秋DFM软件进行阻抗计算,计算方法与上述8层1.6MM通孔一致,不一一截图,计算出的阻抗线宽线距如表1-4所示。

表1-4 8层通孔板1.2mm厚度阻抗设计

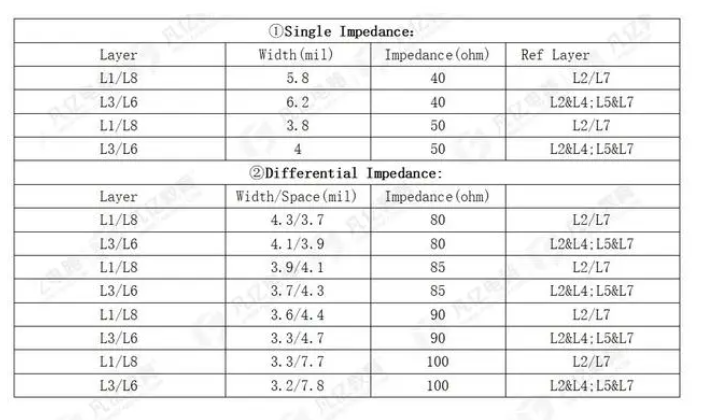

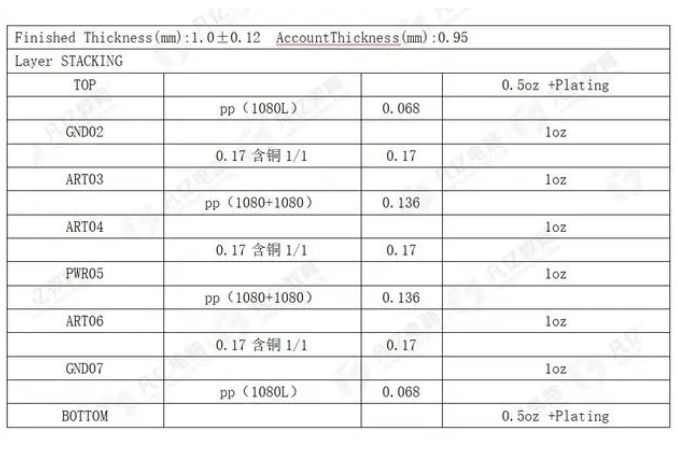

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.0mm,详细的叠层设计如图表1-5所示。

表1-5 8层通孔板1.0mm厚度叠层设计

按照表1-5所示叠层设计参数,使用华秋DFM软件进行阻抗计算,计算方法与上述8层1.6MM通孔一致,不一一截图,计算出的阻抗线宽线距如表1-6所示。

表1-6 8层通孔板1.0mm厚度阻抗设计

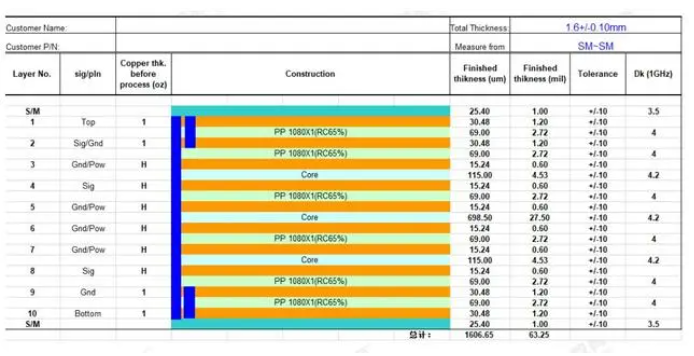

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。建议层叠为

TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建议采用1oZ,其它内层采用HoZ。如图1-13所示为1.6mm板厚的参考叠层。

图1-13 10层1阶HDI板叠层设计

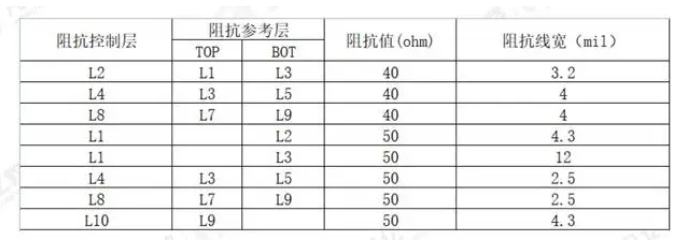

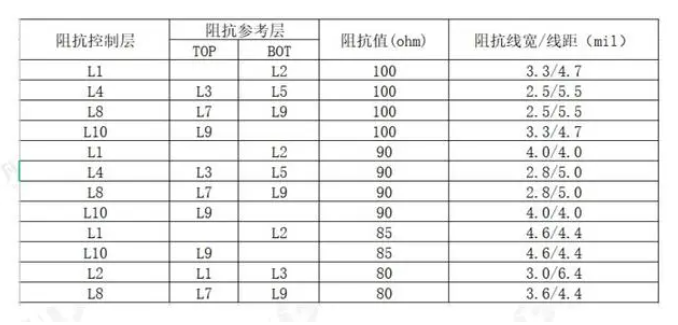

按照图1-13所示叠层设计参数,使用华秋dfm软件进行阻抗计算,计算方法与上述8层通孔一致,不一一截图,计算出的单端阻抗线宽线距如图1-14所示,差分阻抗线宽线距如图1-15所示。

图1-15 10层1阶HDI板单端阻抗设计图

图1-16 10层1阶HDI板差分阻抗设计图

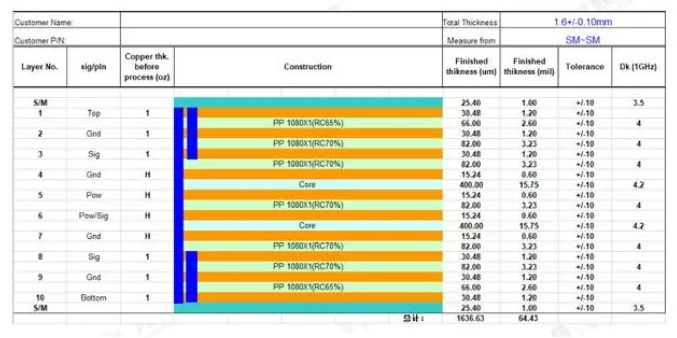

在10层2阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。建议层叠为TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建议采用1oZ,其它内层采用HoZ。图1-17为1.6mm板厚的参考叠层。

图1-17 10层2阶HDI板叠层设计

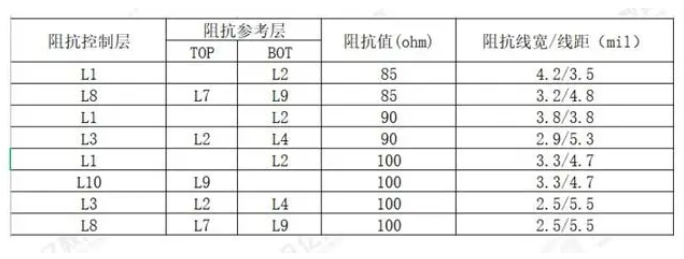

按照图1-17所示叠层设计参数,使用华秋dfm软件进行阻抗计算,计算方法与上述8层通孔一致,不一一截图,计算出的单端阻抗线宽线距如图2-18所示,差分阻抗线宽线距如图1-19所示。

图1-18 10层2阶HDI板单端阻抗设计图

图1-19 10层2阶HDI板差分阻抗设计图

声明:本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注