- 全部

- 默认排序

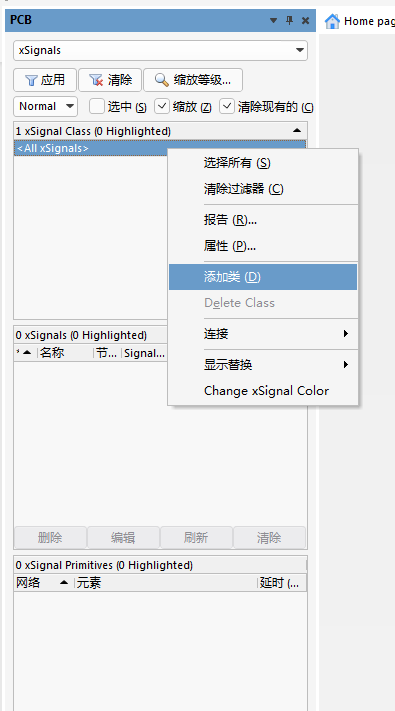

利用Xsignals向导即可自动进行高速设计的长度匹配,它可以自动分析T形分支,元件,信号对和信号组数据,大大减少了高速设计配置时的时间消耗。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

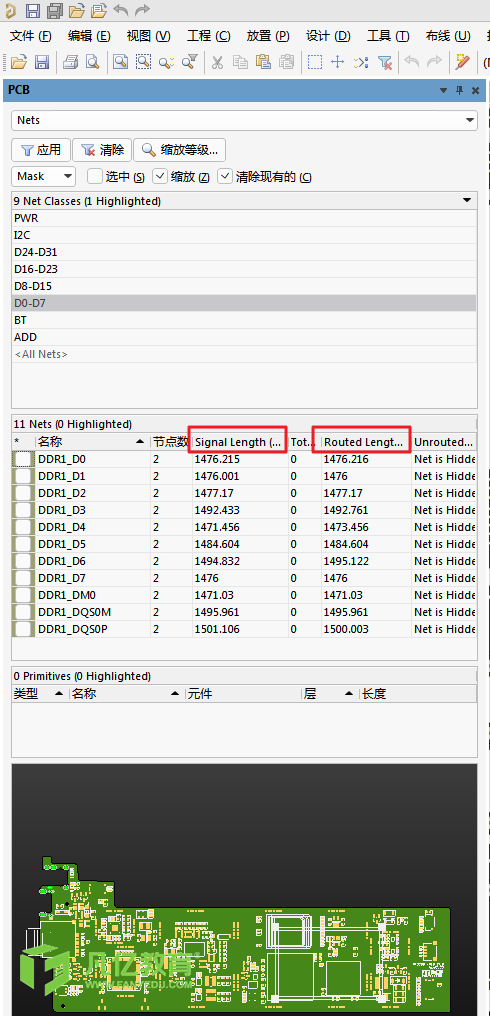

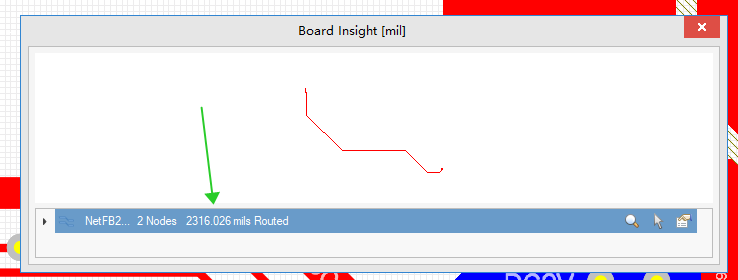

在使用Altium Designer画PCB时,等长布线后,使用快捷键R+L检测布线长度时,发现布的线长不一致,在PCB的nets里查看长度时看到了Signal length和Routed length

SDRAM信号线等长处理

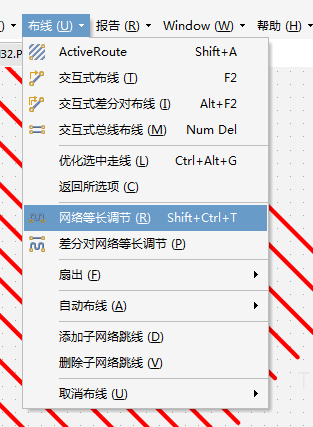

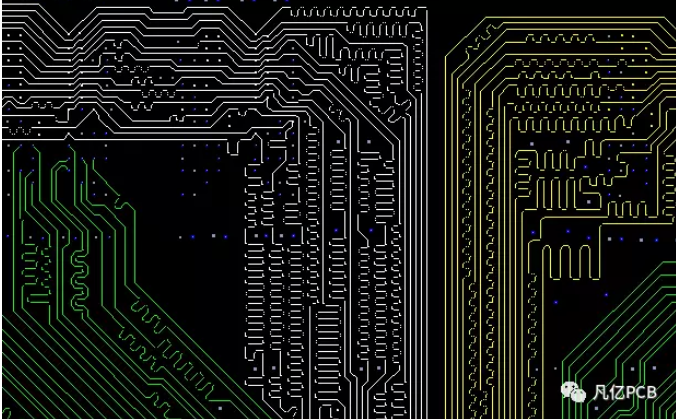

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

PCB设计信号等长分析

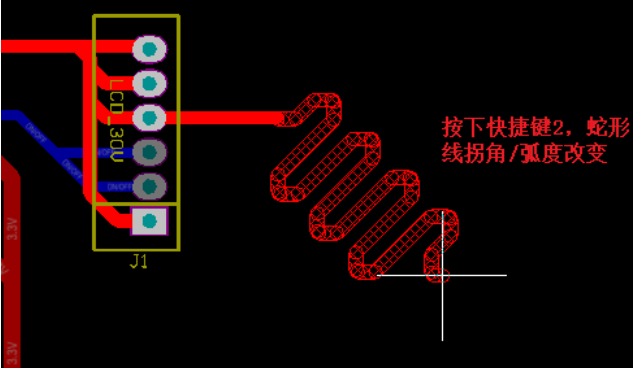

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

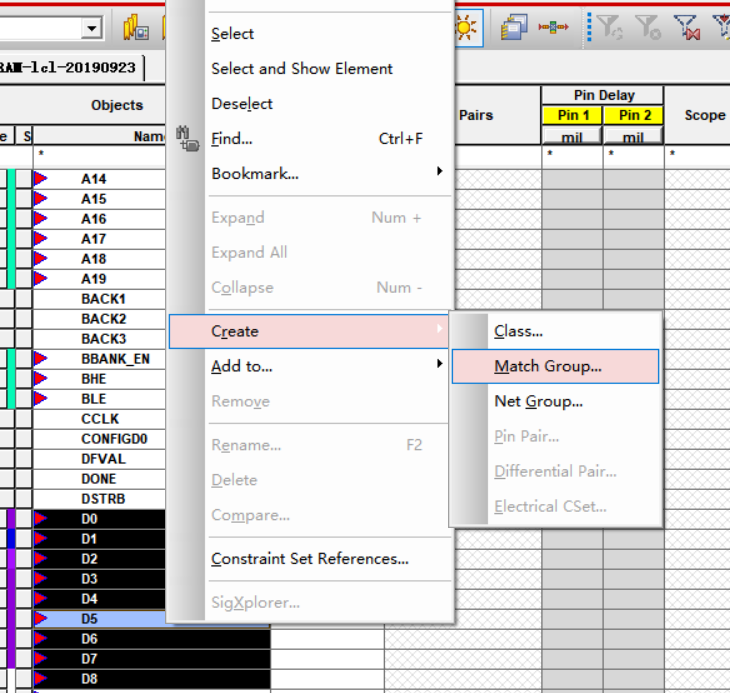

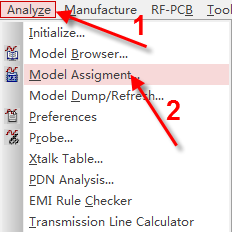

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

扫码关注

扫码关注