- 全部

- 默认排序

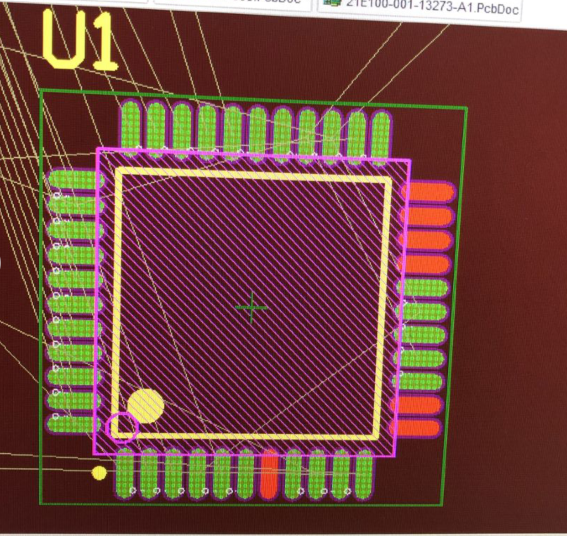

1.首先我们找到警告的相关元器件,例如是这个元器件;2.对该元器件进行双击;此时弹出该元器件的:图形属性窗;此时的designator框中是乱码,我们需要对其进行修改。

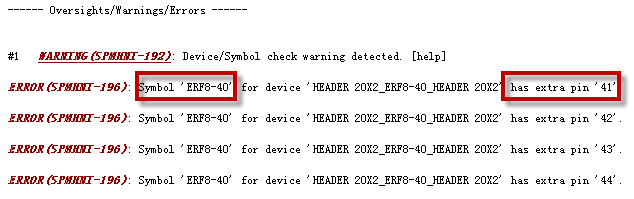

在运行DRC出现报错,怎样解决这个问题Class Document Source Message Time Date No. [Silk To Solder Mask Clearance Constraint Violation] PCB1.PcbDoc Advanced PCB Silk To

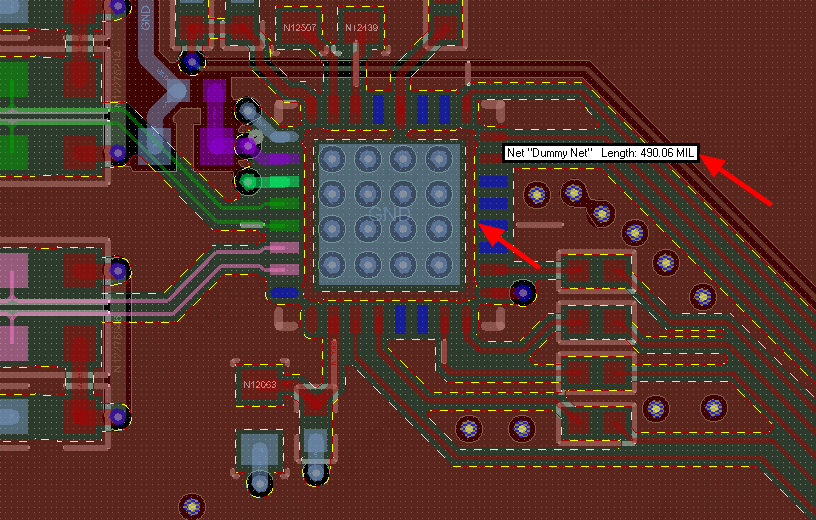

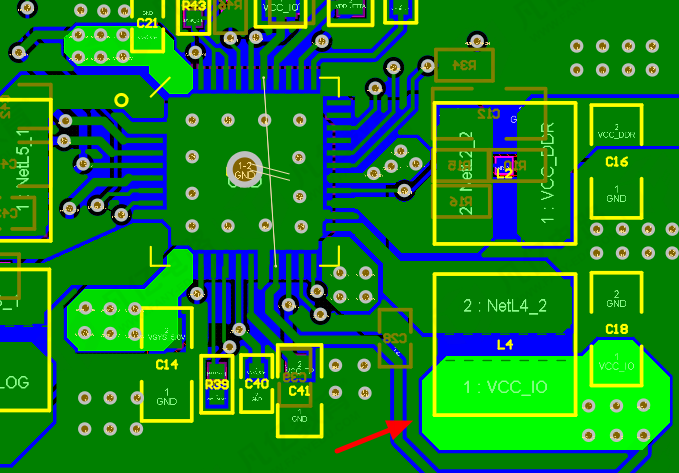

顶层大GND铜皮没有网络,多处孤岛铜皮靠近管脚放置,走线或铺铜直接连接到引脚不要接到电源层多处过孔没有网络,造成天线报错走线到过孔距离太近rx、tx分别建立等长组控100mil误差等长以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

存在报错未处理过孔打到最后一个器件后方多处孤岛铜皮、尖岬铜皮以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?spm

我们在进行PCB设计中,明明在规则约束器里面已经设置过相应的规则了,为什么它就是不进行报错呢?这是为什么?其实很简单,主要是两方面的操作,我们就以AD19为例进行操作吧。

扫码关注

扫码关注