- 全部

- 默认排序

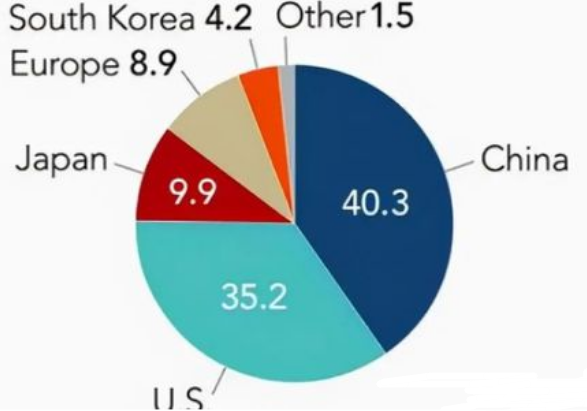

近日,EDA大厂新思科技(Synopsys)因涉嫌向华为海思和中芯国际提供帮助,而被美国商务部调查。引发了许多争议,虽然是关于美国制裁的老生常谈话题,但这也侧面反映我国EDA软件方面的弱势。会EDA软件?能电路设计?懂电路理论?>>《弟子计

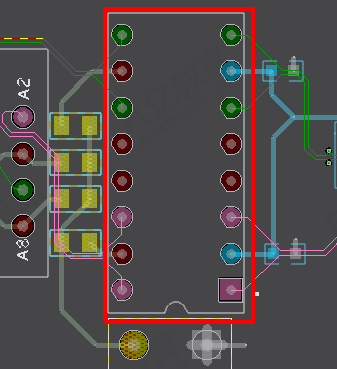

差分信号打孔换层 注意两侧打上地过孔,缩短回流路径:注意器件尽量整体中心对齐:过孔注意间距,不要造成平面割裂:变压器上除了差分信号 其他的加粗20MIL:差分对内等长误差控制在5MIL:RX TX需要对内做等长以上评审报告来源于凡亿教育90

变压器上除了差分信号,其他的加粗20MIL走线:晶振尽量包地处理:RX TX以及差分组内等长没啥问题:建议机壳地与电路地之间分割2MM间距:其他的没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可

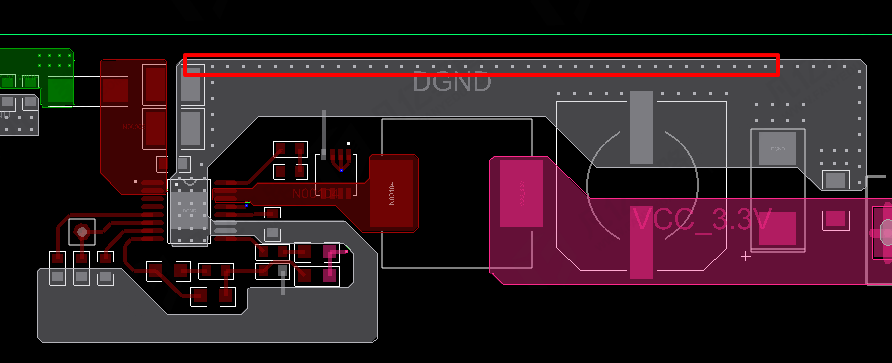

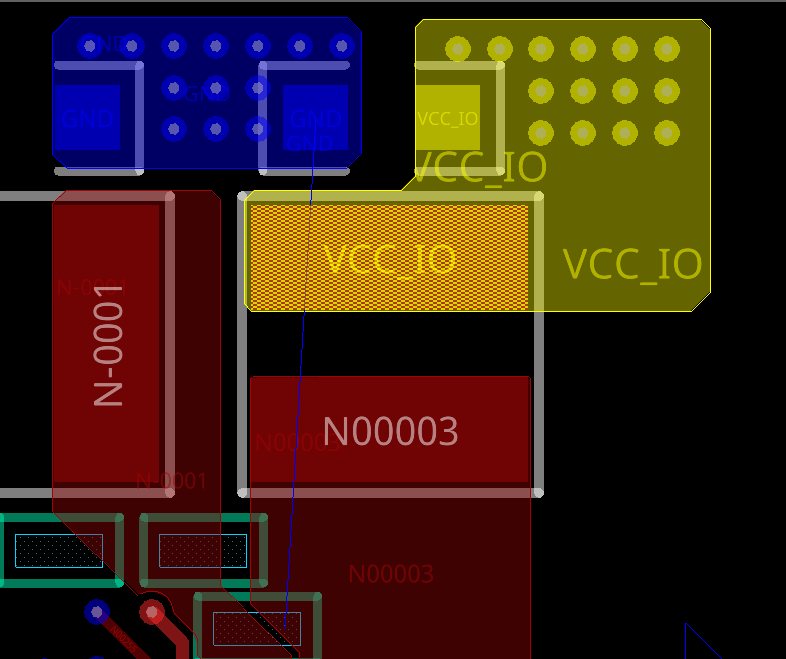

要求单点接地,只在芯片下方打孔连接大GND铜皮相邻电路大电感应朝不同方向垂直放置电源输入打孔应在第一个器件前方,经过第一个电容在到后方器件存在多处飞线没有连接反馈信号应连接到电路最后一个器件底层应大面积铺GND网络铜皮以上评审报告来源于凡亿

要求单点接地,gnd网络都连接到芯片下方打孔,其他地方不要打孔器件按照先大后小原则布局,先经过大器件在连接到小器件相邻电路大电感朝不同方向垂直放置大电感下方挖空所有层铺铜存在飞线,电源没有连通器件尽量中心对齐以上评审报告来源于凡亿教育90天

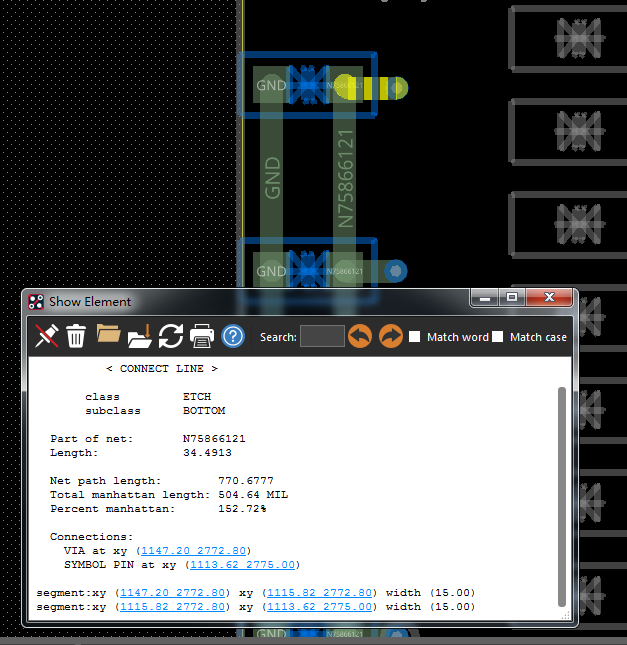

还存在飞线,注意电源信号处理:差分打孔换层的过孔两边注意添加地过孔,缩短回流路径:注意差分对内等长误差为5MIL:差分组跟组不用等长,组内等长就可以了:单端信号的TX RX需要组内等长,没有设置:自己后期去设置下组内等长,在拉等长。以上评审

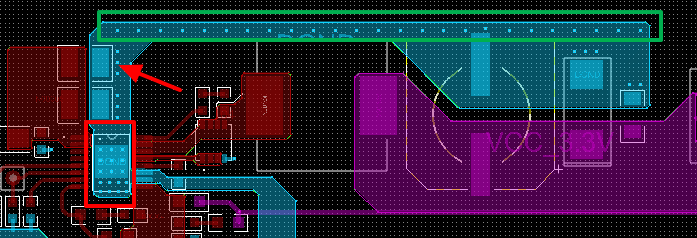

变压器下方所有层挖空铺铜差分换层打孔旁边要打回流地过孔差分对内等长绕线错误差分对内等长误差控制5mil范围内以太网转换芯片到CPU的tx、rx网络走线分别建立等长组,控100mil误差范围分别等长。电源输入接到第一个电容前方,在从最后一个电

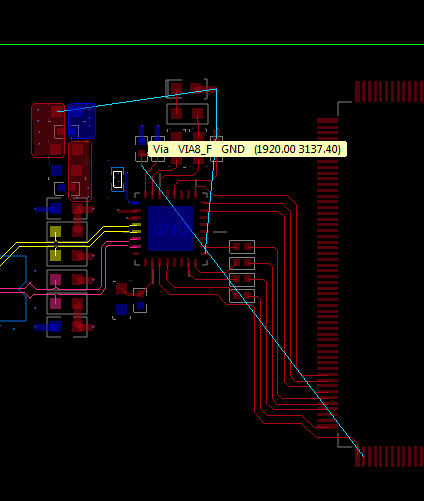

还有地网络并未处理,还有飞线:对应器件就近管脚放置:过孔数量根据载流大小计算下个数,再加2-4个过孔的裕量就可以了:底层器件尽量整体中心对齐放置:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

据外媒报道,今年年初,美国和日本合作制定5G标准后,正佳加快速度推进这一计划,争取在2024年共同推出6G标准,这项行为或将促使中国和欧洲再度合作制定6G标准。欲成射频工程师,来凡亿教育!活动特惠!满300-30!《弟子计划:毫米波天线阵列

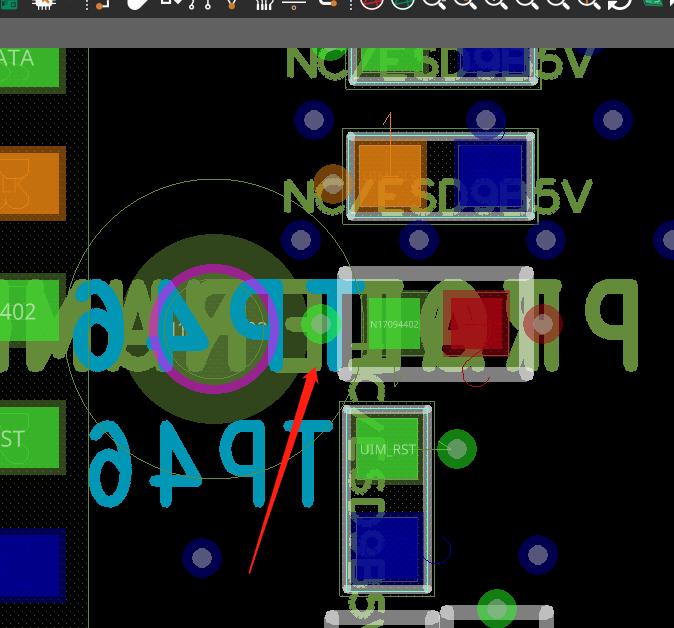

SIM:注意测试点跟器件以及过孔的间距,此处右侧器件可以整体往右边挪动一点:注意铜皮尽量设置动态铜皮,将静态转换下:电感内部挖空掉,在当前层:TF:注意器件之间可以空出点间距留出来扇孔,扇孔不要离焊盘太远:时钟信号包地保全一点,还有 空间可

全站最新内容推荐

- 1USB2.0实际传输速度为什么与480Mbps相差甚远

- 2RSC6218A LLC谐振电源案例分享-REASUNOS(瑞森半导体)

- 3现场可编程门阵列 (FPGA) XCVU5P-L2FLVA2104E、XCVU5P-2FLVA2104I支持 3D IC 技术的高性能 FPGA

- 4示波器探头校准-补偿电容

- 5铝电解电容的ESR到底是多少呢?

- 6汽车总线除了CAN,还有LIN总线

- 7LCD液晶段码显示驱动IC-VKL060超低功耗/低电流/省电液晶显示驱动芯片

- 8配置两个dsPIC DSC内核,DSPIC33CH128MP505-E/PT / DSPIC33CH128MP505-E/PTVAO 双核数字信号控制器

- 9电动汽车EMC的中国标准体系有哪些?

- 10教你如何区分云数据迁移/分层

扫码关注

扫码关注