- 全部

- 默认排序

1、了解平板电脑的设计总体要求及设计框架 2、掌握电子设计的流程化设计 3、了解设计当中涉及到的基本概念 4、掌握PCB设计的布局布线规划 5、 掌握软件模块化布局技巧 6、掌握各类接口器件和功能模块的布局布线要点 7、常见EMC/EMI的处理方式及注意事项

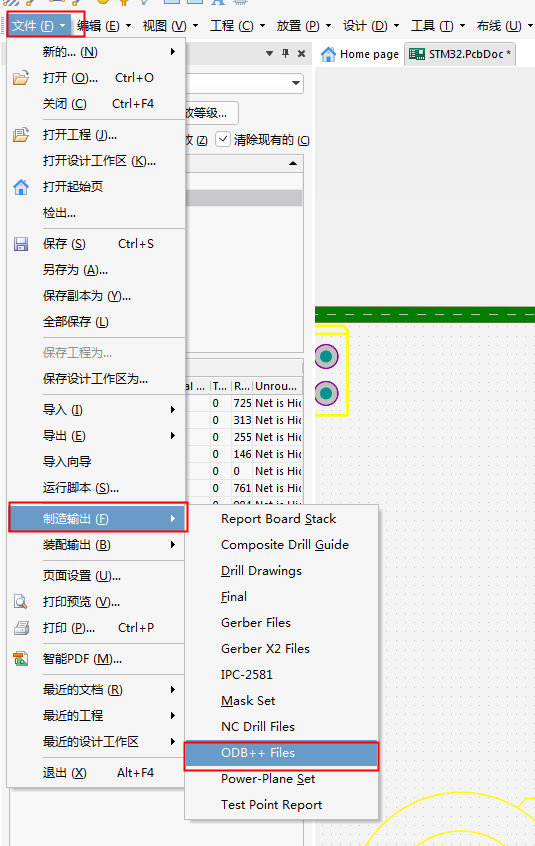

ODB++文件是由VALOR(IPC会员单位)提出的一种ASCII码,双向传输文件。文件集成了所有PCB和线路板装配功能性描述。涵盖了PCB设计、制造和装配方面的要求。包括所有PCB绘图、布线层、布线图、焊盘堆叠、夹具等所有信息。它的提出用来代替GEBER文件的不足,包含有更多的制造、装配信息。

随着FPGA的不断开发,其功能越来越强大,也给其布线带来了很大的便捷性—管脚的调整。 对于密集的板卡,走线时可以不再绕来绕去,而是根据走线的顺序进行信号的调整,然后通过软件编程来校正信号的通信就可以了。在调整FPGA管脚之前必须熟悉几点注意事项。

本次直播我们将以cadence allegro 17.4来详细讲解一个GD32 ARM开发板整个开发过程,从原理图设计、PCB 3D封装创建、到PCB布局布线整个过程,由于时间比较长, 本次直播将分为8期来进行讲解,具体时间安排请查看下面的时间直播排期表。

我想请问一下,我PCB布线的时候出现报错提示 “用于开始布线的项目为选定”这里的意思是筛选没有选择对吗?

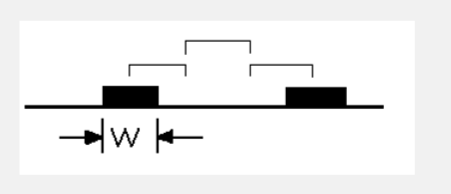

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

扫码关注

扫码关注