- 全部

- 默认排序

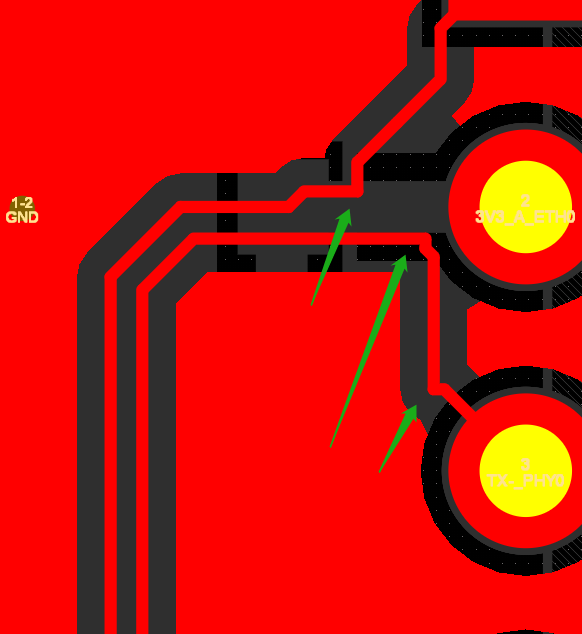

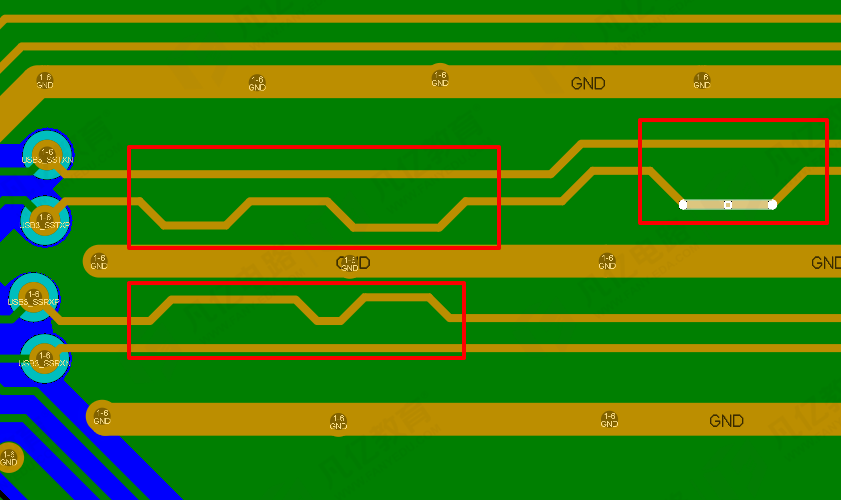

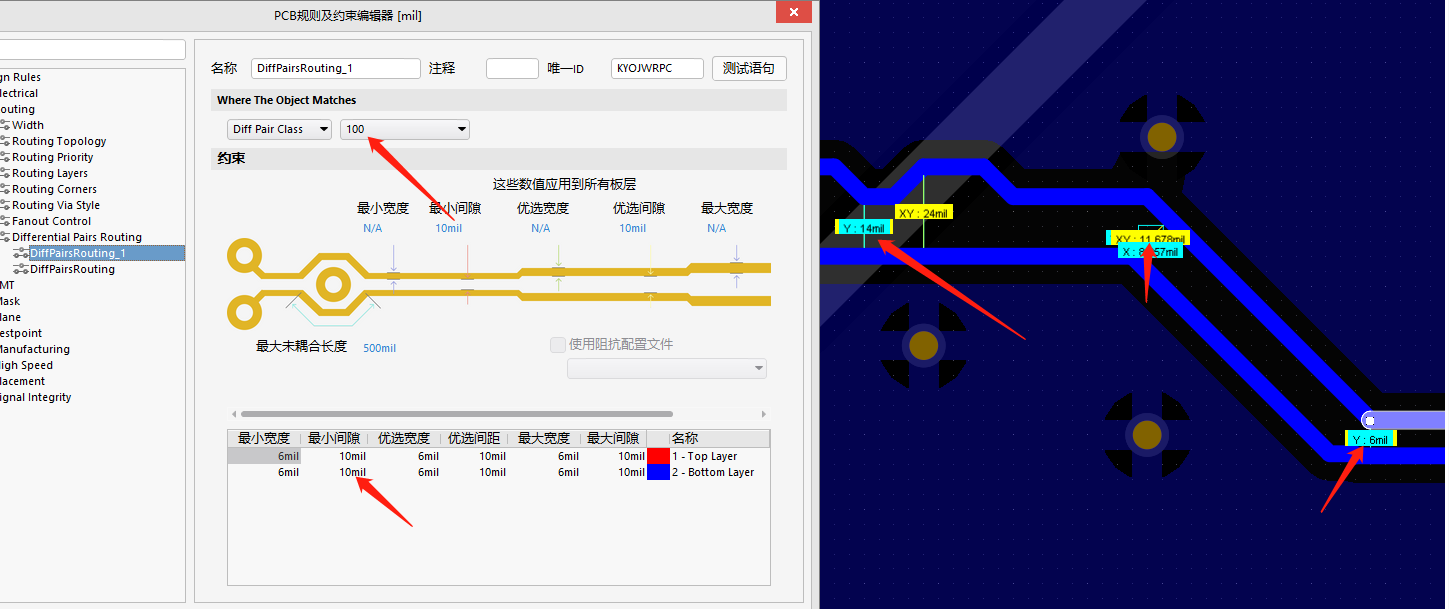

差分线都不合格,都存在直角:完全是不允许的,需要删除重新走线。上面那组差分出现,需要跟下面那组一样,下面的差分是完全合格的耦合走线:焊盘不能随意出现,需要从中心往两长边拉线:差分对内等长误差为5MIL:单端线等长改下等长模式,也是不能直角:

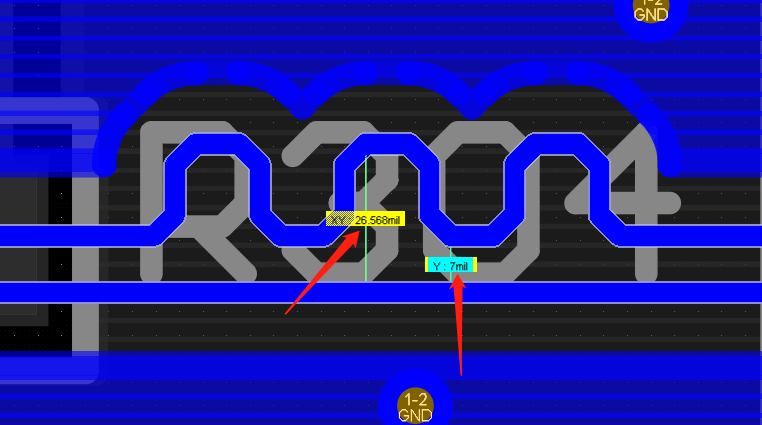

注意差分对内等长凸起高度不能超过线距的两倍差分尽量哪里不耦合就在哪里绕,尽量不要在中间绕蛇形2.差分出线需要耦合,后期自己调整一下3.走线尽量不要有锐角,后期自己优化一下4.时钟信号需要包地处理,并在地线上打孔,建议50-100mil一个以

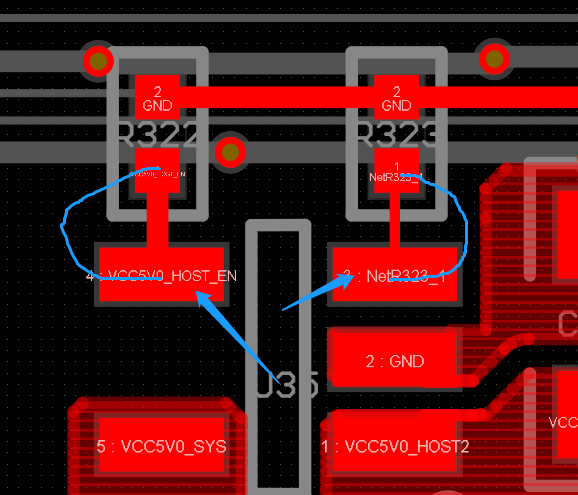

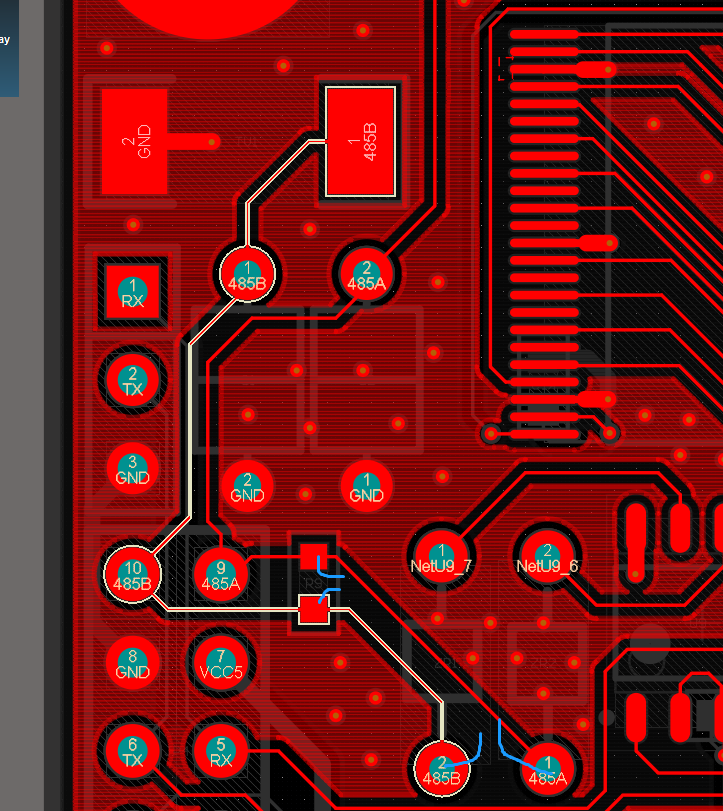

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.差分线处理不当,锯齿状等长不能超过线距的两倍3.差分对内等长误差5mil4.此处需要经过ESD器件在到USB座子5.地网络直接就近打孔即可以上评审报告来源于凡亿教育90天高

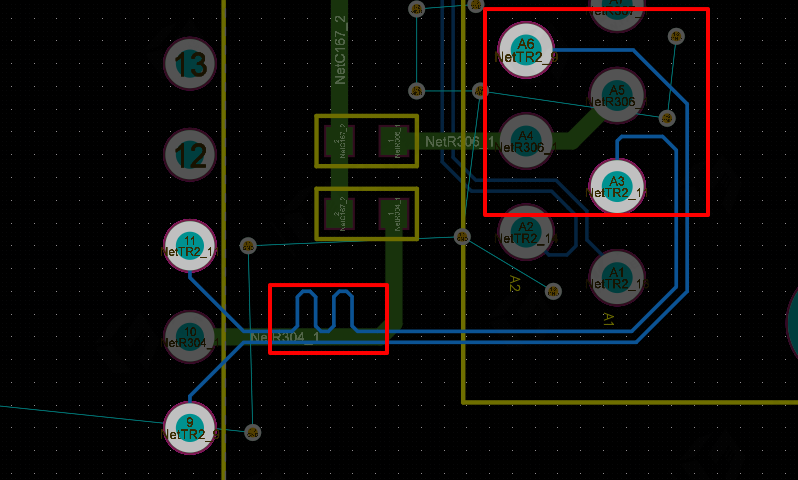

差分走线需要保持耦合从过孔内拉出:此处差分亚需要重新拉出耦合走线,并且差分对内等长需要注意规范:注意高度要小于2S。板上多余线头删除掉:其他的没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

变压器下方所有层挖空铺铜差分换层打孔旁边要打回流地过孔差分对内等长绕线错误差分对内等长误差控制5mil范围内以太网转换芯片到CPU的tx、rx网络走线分别建立等长组,控100mil误差范围分别等长。电源输入接到第一个电容前方,在从最后一个电

差分等长错误:1.尽量在引起不等长端绕线 2.差分对内等长绕线高度和间距不规范地址线要单根包地打孔处理tx、rx分别建立等长组等长,两组走线之间保持4w间距,有空间单组包地或两组包地以上评审报告

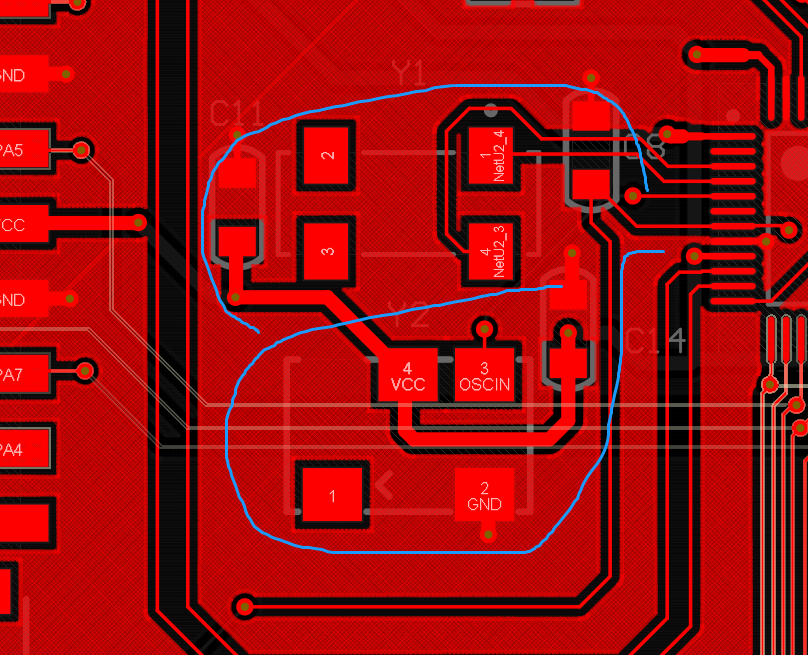

晶振需要包地处理,并且晶振下面不要走线2.走线不要从小器件中间穿,后期容易造成短路3.封装焊盘移位,后期不能进行焊接器件,后期自己检查一下4.RS232的升压电容走线需要加粗5.USB需要控90欧姆的阻抗,对内等长误差5mil,后期自己处理

1.485信号需要走内差分处理,后期自己调整一下布局,然后重新走线2.晶振优先布局,走线路劲要尽量短3.晶振注意电容摆放顺序,先经过电容,在到晶振4.差分出线要耦合,走线尽量不要走小器件中间,容易造成短路5.差分对内等长处理不当,锯齿状等长

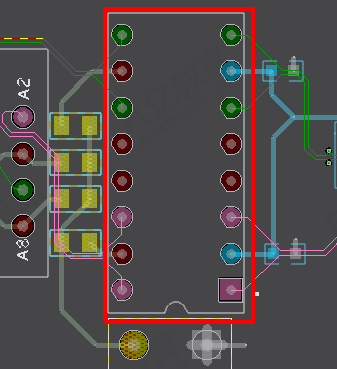

差分对内等长不符合规范兼容器件这样布局差分换层旁边打回流地过孔电容按照先大后小原则放置差分对内等长控制5mil以内差分包地不完整,朝外边也需要打孔差分走线出焊盘后尽快耦合以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

扫码关注

扫码关注