- 全部

- 默认排序

问:一般接口ESD处理方式都是,ESD防护器件一端接电源或信号,另一端接GND或PGND。产品在接地时还好理解,ESD器件将干扰导入到大地;当产品不接地时,ESD器件将干扰导入到GND,虽然GND平面与大地之间有寄生电容可以泄防一部分ESD

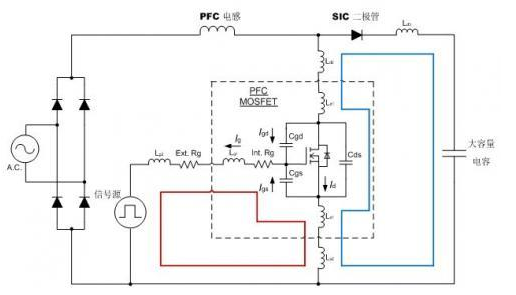

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC

在高频电路设计中,寄生电容的存在是很重要的,它是指在电路中不期望存在的电容,通常是由电路元件之间的绝缘层、导线、接头等产生,它的存在会导致电路的频率响应、增益和相位等特征发生变化,甚至无法正常工作,所以降低RF电容的寄生电容是很有必要的。1

同步BUCK降压变化器是应用非常广泛的一种电源结构,其工作频率由早期的低于100KHz,提高到200KHz、300KHz、350KHz、500KHz、1MHz,甚至更高,工作频率的提高带来的好处是电源系统的体积降低,但是,缺点就是开关损耗会增加。功率MOSFET在进一步减小导通电阻、降低导通损耗的同

在高速PCB设计中,寄生电感和噪声问题是常见的挑战,寄生电感是指电流在导体中产生的磁场所形成的电感,将影响信号的传输速度和稳定性,尤其是在高速PCB中更加明显,噪声问题也一样会对信号传输和系统性能产生负面影响。因此,在高速PCB设计中,需要

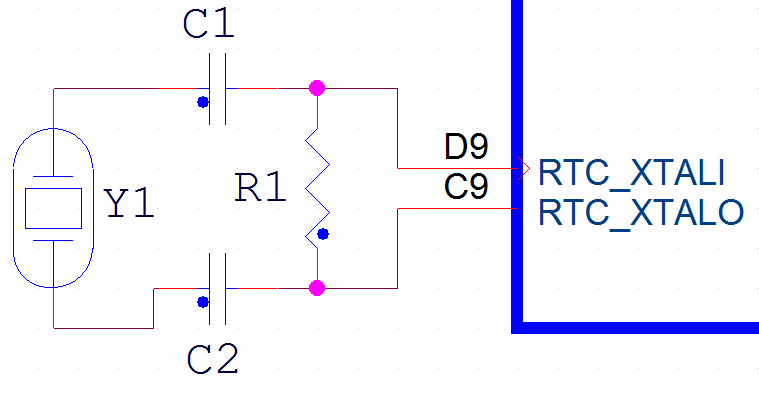

PCB设计中晶体的π型滤波应该怎么设计?答:在晶体的电路设计中一般都采用π型滤波来进行设计,原理图设计部分如图1-41所示,后期我们在进行PCB布局布线的时候,要注意以下几点:布局整体紧凑,一般放置在主控的同一侧,靠近主控IC,尽量不要靠近板边;布局是尽量使电容分支要短,目的是为了减小寄生电容;晶振电路一般采用π型滤波形式,放置在晶振的前面;晶体和晶振的布局要注意远离大功率的元器件、散热器等发热的器件。其原理图设计部分如图1-41所示。 图1-41 晶体π型滤波电路示意图其PCB设计部

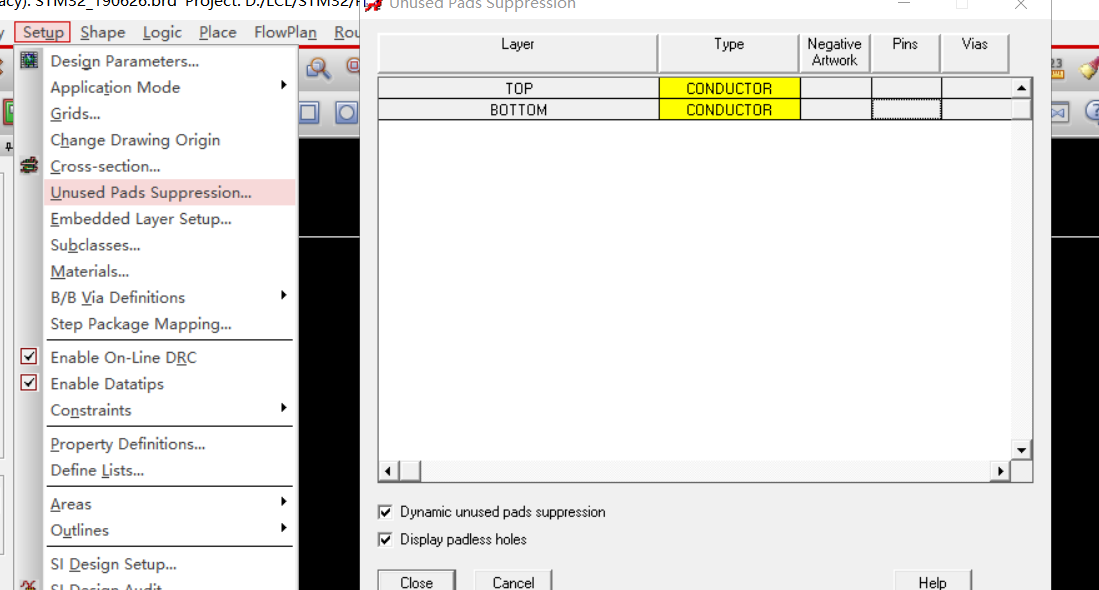

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

扫码关注

扫码关注