- 全部

- 默认排序

寄生电容在集成电路是无处不在,但若电路设计对电容敏感度低可忽略寄生电容带来的影响,但若电路设计要求芯片速度快或频率高,寄生电容将十分重要,所以若是遇见这个情况,该如何减小寄生电容带来的影响?首先需要知道的是,若模拟电路频率一旦超频率20MH

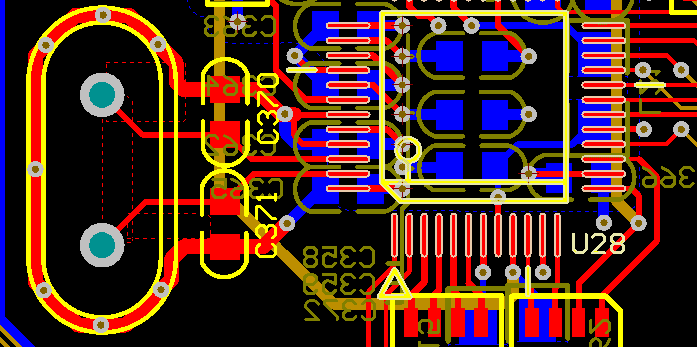

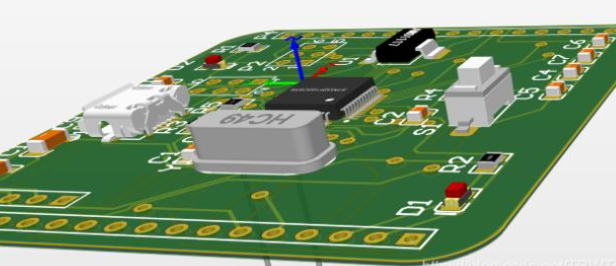

关于PCB设计中晶体晶振的布局和布线要求,布局要求:1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。2、布局是尽量使电容分支要短(目的:减小寄生电容,)

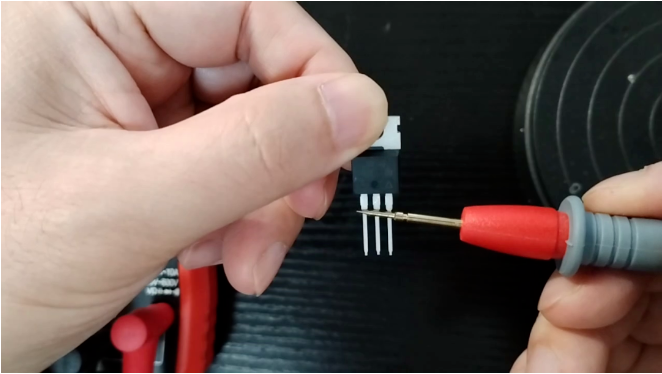

利用场管内部的寄生二极管的单向导通特性对场管的好坏进行判断。第一步 将三个脚进行短接放电这样做的目的对场管内部的寄生电容进行放电,防止有压差,使它内部产生导通,使得测量有误。第二步 测量内部二极管万用表打到二极管档,然后用两个表笔对这个 M

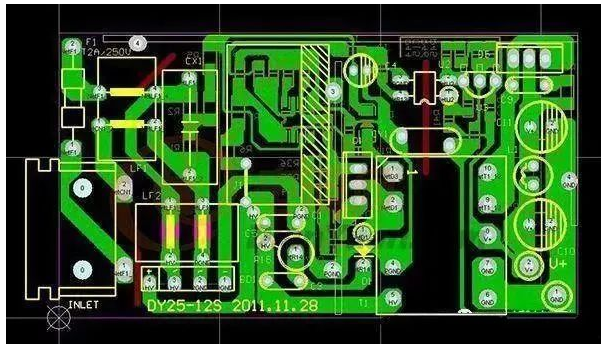

许多设计人员习惯于根据电路模型来思考系统行为。这些模型和电路图在某种程度上都是正确的,但是它们缺少一些确定系统行为的重要信息。电路图中缺少的信息是实际PCB布局的几何形状,它决定了系统中的元素如何相互电和磁耦合。那么,是什么导致真正的PCB

答:过孔的两个寄生参数是寄生电容和寄生电感。过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为T,板基材介电常数为ε,则过孔的寄生电容大小近似可以用以下公式来计算:C=1.41εTD1/(D2-D1)。过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50Mil的PCB板,如果使用内径为10Mil,焊盘直径为20Mil的过孔,焊盘与地铺铜区的距离为32Mil,则我们可以通过上面的公式近似

模块化电路设计有两方面的含义,其一是指电路设计功率器件的模块化,其二是指电源单元的模块化。我们常见的元器件器件模块,含有一单元、两单元、六单元直至七元,包括开关器件和与之反并联的续流二极管,实质上都属于“标准”功率模块(SPM)。近年,有些公司把开关器件的驱动保护电路也装到功率模块中去,构成了“智能化”功率模块(IPM),不但缩小了整机的体积,更方便了整机的电路设计制造。实际上,由于频率的不断提高,致使引线寄生电感、寄生电容的影响愈加严重,对器件造成更大的电应力(表现为过电压、过电流毛刺)。为了

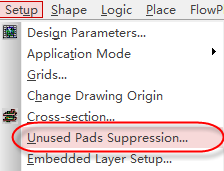

答:做无盘设计的目的,是因为通孔的焊盘在内电层,是具有寄生电容的效应的,容易造成阻抗的不连续,导致信号出现发射,从而影响信号的完整性,所以在处理高速信号时候,在PCB设计端就将走线连接层的焊盘去掉,最大程度的保持地过孔与通孔连接处的走线阻抗一致,具体操作的步骤如下所示:

问:一般接口ESD处理方式都是,ESD防护器件一端接电源或信号,另一端接GND或PGND。产品在接地时还好理解,ESD器件将干扰导入到大地;当产品不接地时,ESD器件将干扰导入到GND,虽然GND平面与大地之间有寄生电容可以泄防一部分ESD

SiC MOSFET沟槽结构将栅极埋入基体中形成垂直沟道,尽管其工艺复杂,单元一致性比平面结构差。但是,沟槽结构可以增加单元密度,没有JFET效应,寄生电容更小,开关速度快,开关损耗非常低;而且,通过选取合适沟道晶面以及优化设计的结构,可以实现最佳的沟道迁移率,明显降低导通电阻,因此,新一代SiC

扫码关注

扫码关注