- 全部

- 默认排序

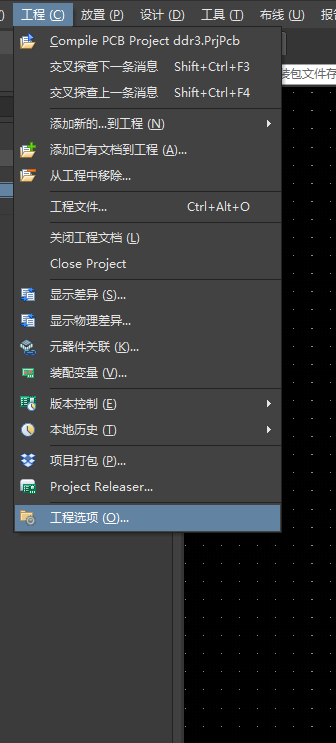

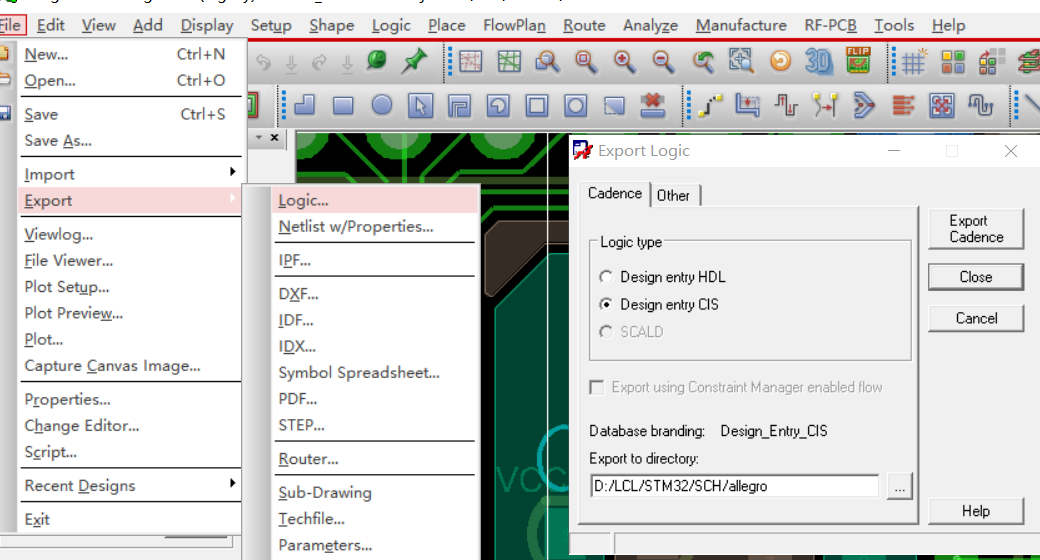

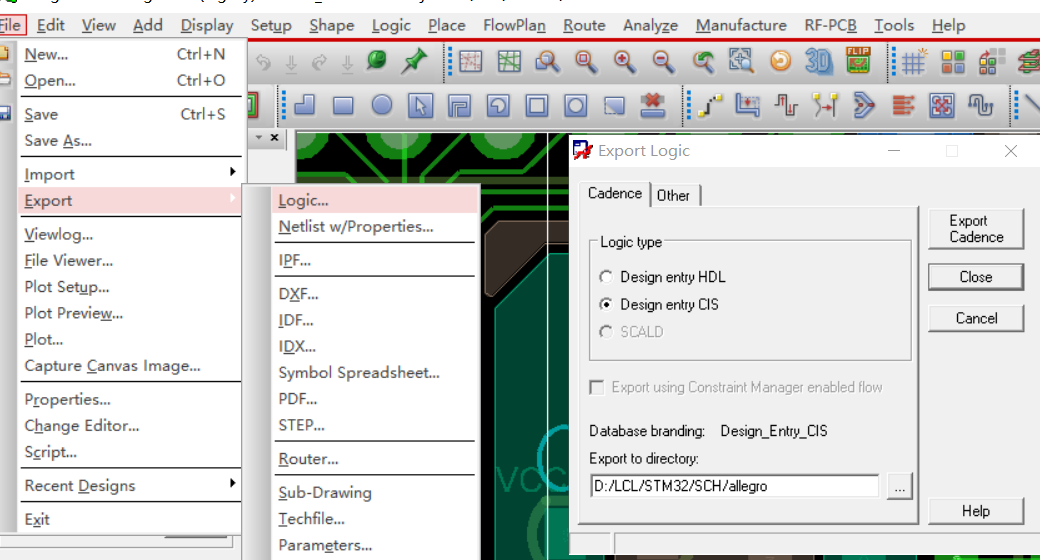

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。导出完毕后,单击close按钮,关闭对话框。用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

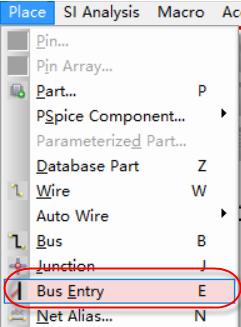

我们创建好总线,给总线命名好以后就需要将创建好的总线与个分支信号连接起来,操作的步骤如下所示:第一步,放置总线入口Bus Entry,点击菜单Place→Bus Entry或者按快捷键E来进行放置,如图3-28所示;第二步,Bus Entry会悬挂在鼠标上,按快捷R可以进行旋转,选择好正确的方向,然后放置到总线上,与总线进行连接,如图3-28所示;第三步,在放置Bus Entry的时候,放置好一个以后,按快捷键F4可以进行快速放置,也可按住Ctrl键,鼠标拖动来进行快速放置,如图3-28所示;&

1.Altium Designer将需要做等长的线组成一个类:在Design-Classes中,右键Net Classes弹出菜单中,选择Add Class,为新New Class命名(Rename Class),加入需要的Net。

接口设计及网络命名

在Logic软件中使用Bus总线的时候,有以下几个注意事项:第一,总线不是强制使用的,不使用总线也是可以的,使用总线构架是使得原理图更加清晰,分析原理图更加透彻,第二,总线命名方式一定要按照如 Busname[00:24]这种方式,然后信号分支网络标号的命名方式与总线保持一致。

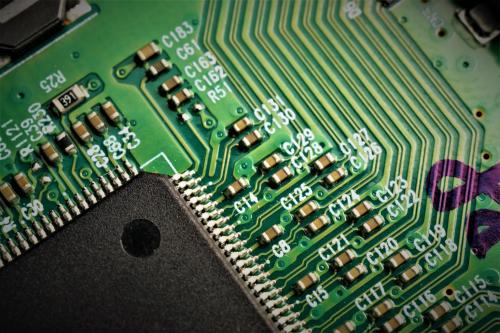

什么是总线,是指一组具有相关性的信号线,在原理图中使用较粗的线条走线代表总线。针对于这一组一组的总线网络,主要是为了原理图查看方便,我们一般会加上总线的结构。

在LAYOUT中制作PCB封装时,在遇到焊盘管脚需要重新命名时,是有小技巧可以快速修改的。这个小视频介绍了封装焊盘管脚重新重名的小技巧。

扫码关注

扫码关注