- 全部

- 默认排序

1 层叠的定义及添加对高速多层板来说,默认的两层设计无法满足布线信号质量及走线密度要求,这个时候需要对PCB层叠进行添加,以满足设计的要求。2正片层与负片层正片层就是平常用于走线的信号层(直观上看到的地方就是铜线),可以用“线”“铜皮”等进行大块铺铜与填充操作,如图8-32所示。图8-32 正片层

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到八层板的叠层来进行示例讲解单面PCB板和双面PCB板的叠层对于两层

答:在生成的Gerber中,除了要将PCB上的走线、过孔等内容包含进去,还需要将PCB的叠层等信息制作进去,以便提供详细的文件给工厂生产,Allegro提供了一个直接提取设计参数生成的叠层表格的功能,减少了设计者的工作量。

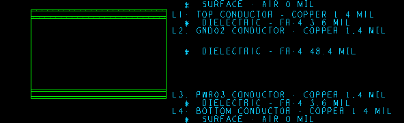

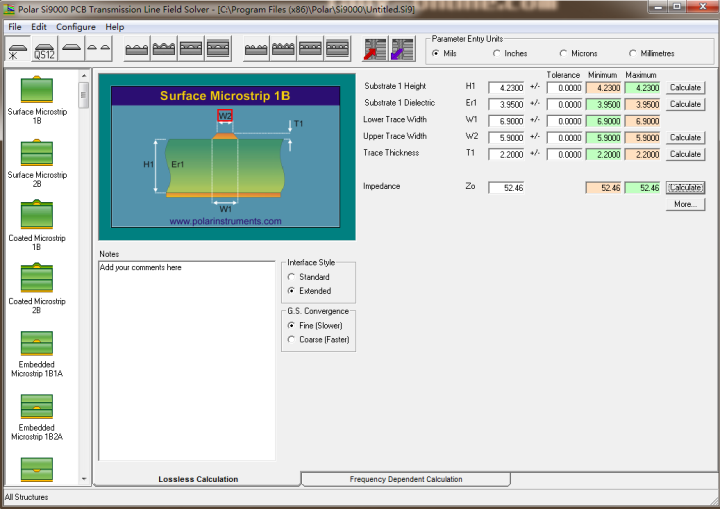

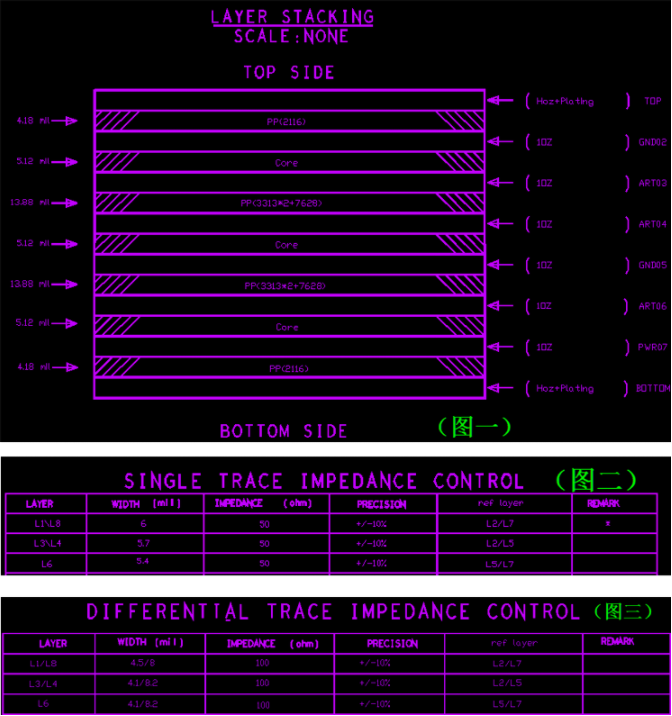

特性阻抗,体现在PCB板上,主要是通过叠层、线宽、线距。在PCB版图布局完成以后,我们要对PCB板进行层叠设计,将PCB板按照一定的厚度叠好以后,根据层叠结构,通过SI9000这个软件来进行阻抗线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。TOP0.5oz +PlatingPP(2116)4.23GND021ozCore20.08ART031ozPP(1080*2)4.59PWR041ozCore20.08GND0

SiP失效模式和失效机理

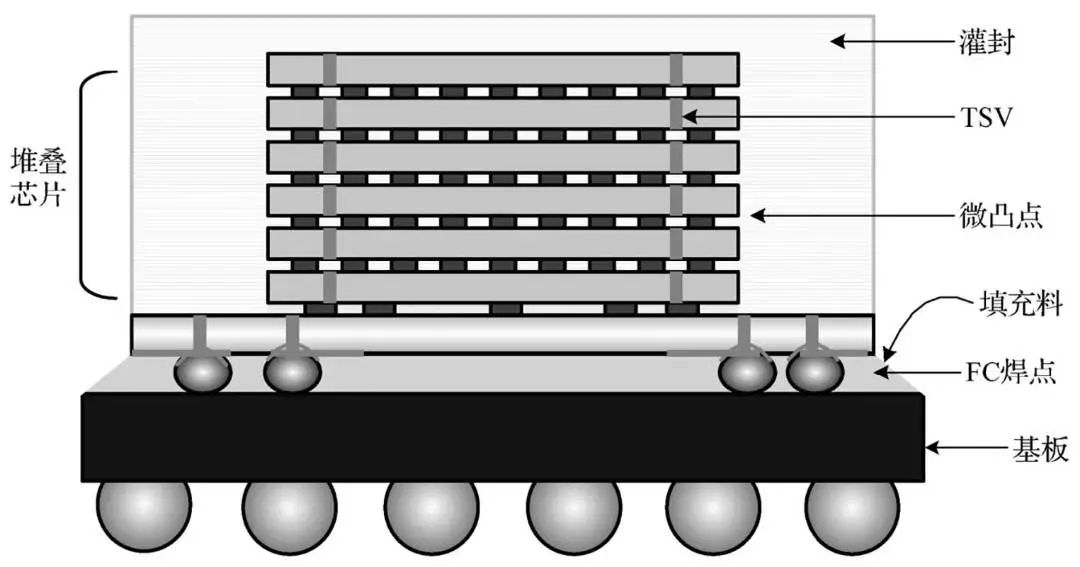

SiP组件的失效模式主要表现为硅通孔(TSV)失效、裸芯片叠层封装失效、堆叠封装(PoP)结构失效、芯片倒装焊失效等,这些SiP的高密度封装结构失效是导致SiP产品性能失效的重要原因。一、TSV失效模式和机理TSV是SiP组件中一种系统级架构的新的高密度内部互连方式,采用TSV通孔互连的堆叠芯片封装

什么是阻抗?多层板应该怎么去叠?PCB走线应该走多粗?这些问题是不是很熟悉,这是很多工程师的老大难问题,其实这就是没有搞清楚叠层跟阻抗的问题。我们本次直播全面剖析多层板的叠层控制以及阻抗如何计算,教会大家轻松解决高速PCB设计中的阻抗与叠层。

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。这就是设计多层板一个简单概念。 确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,一个好的叠层设计方案将会

需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图示)。设计的线宽线距应该考虑所选PCB生产工厂的生产工艺

扫码关注

扫码关注