- 全部

- 默认排序

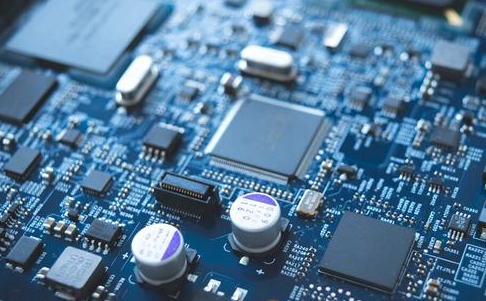

为抑制电磁干扰(EMI),很多优秀的PCB设计工程师会选择在新的设计中挑选最合适的集成电路芯片,以此达到最佳的EMI抑制的性能,同时还会将去耦电容直接放在IC封装内来有效控制EMI并提高信号完整性。但是很多小白可能不太清楚IC封装的EMI控

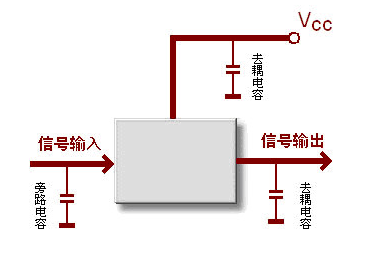

为保证印制电路板(PCB板)能够处在最佳状态上运行,很多工程师会选择设计电路来提高PCB板的可靠性,一般会采用去耦电容来配置,但是有一部分小白可能不太清楚如何操作,所以本文将谈谈如何通过去耦电容配置来提高PCB板的可靠性设计。在直流电源回路

之前更新了《多层印制电路板(PCB)的电磁兼容性设计指南(上)》,反响不俗,今天更新下篇,希望对小伙伴们有所帮助,还有更多问题可在下方留言哦!4、旁路电容与去耦电容的设计设计PCB时经常要在电路上加电容器来满足数字电路工作时要求的电源平稳和

为什么总是在电路里摆两个0.1uF和0.01uF的电容?01 旁路和去耦旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。要理解这两个词汇

随着微电子技术的发展,越来越多的电子产品急需高性能来处理高数据量问题,这也促使电路设计愈发复杂,以适应多种不同的需求变化,这也充分考验电子工程师的设计能力和理论能力。其中之一是电路设计时应如何配置去耦电容?在直流电源回路中,负载的变化都会引

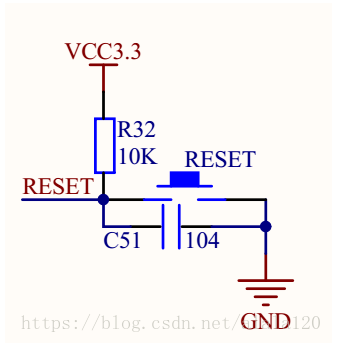

0组成:电源 复位 时钟 调试接口 启动1、电源 : 一般3.3V LDO供电 加多个0.01uf去耦电容2、复位:有三种复位方式:上电复位、手动复位、程序自动复位通常低电平复位:(51单片机高电平复位,电容电阻位置调换)上电复位,在上电瞬

如何测量电源纹波?

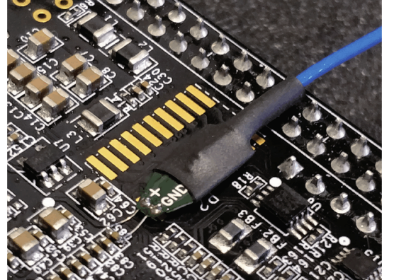

今天聊一聊如何测量电源的纹波。1 纹波的测量点要求纹波测量点要选择靠近负载的地方,例如CPU的供电管脚上的去耦电容上。PDN是一个网络,主板上一个电源平面的不同的地方纹波是不一样的,建议选择最远,负载最大,环境最恶劣的地方。如果一个电源网络

今天的许多设计都包括三个不同值的去耦电容器,或者当只使用一个电容器时,可以使用 0.1 uF 这样的小值。这些建议基于 50 年前不适用的假设。是时候重新考虑这些过时的遗留设计指南了。作为遗留问题的神话从一开始,电子行业就被更快、更小、更便

答:可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容,称做“旁路电容”。 对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除。 去耦电容是电路中装设在元件的电源端的电容,此电容可以提供较稳定的电源,同时也可以降低元件耦合到电源端的噪声,间接可以减少其他元件受此元件噪声的影响。去耦和旁路都可以看作滤波。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电

扫码关注

扫码关注