- 全部

- 默认排序

答:特性阻抗:又称“特征阻抗”,它不是直流电阻,属于长线传输中的概念。在高频范围内,信号传输过程中,信号沿到达的地方,信号线和参考平面(电源或地平面)间由于电场的建立,会产生一个瞬间电流,如果传输线是各向同性的,那么只要信号在传输,就始终存在一个电流I,而如果信号的输出电平为V,在信号传输过程中,传输线就会等效成一个电阻,大小为V/I,把这个等效的电阻称为传输线的特性阻抗Z。信号在传输的过程中,如果传输路径上的特性阻抗发生变化,信号就会在阻抗不连续的结点产生反射。影响特性阻抗的因素有:介电常数、

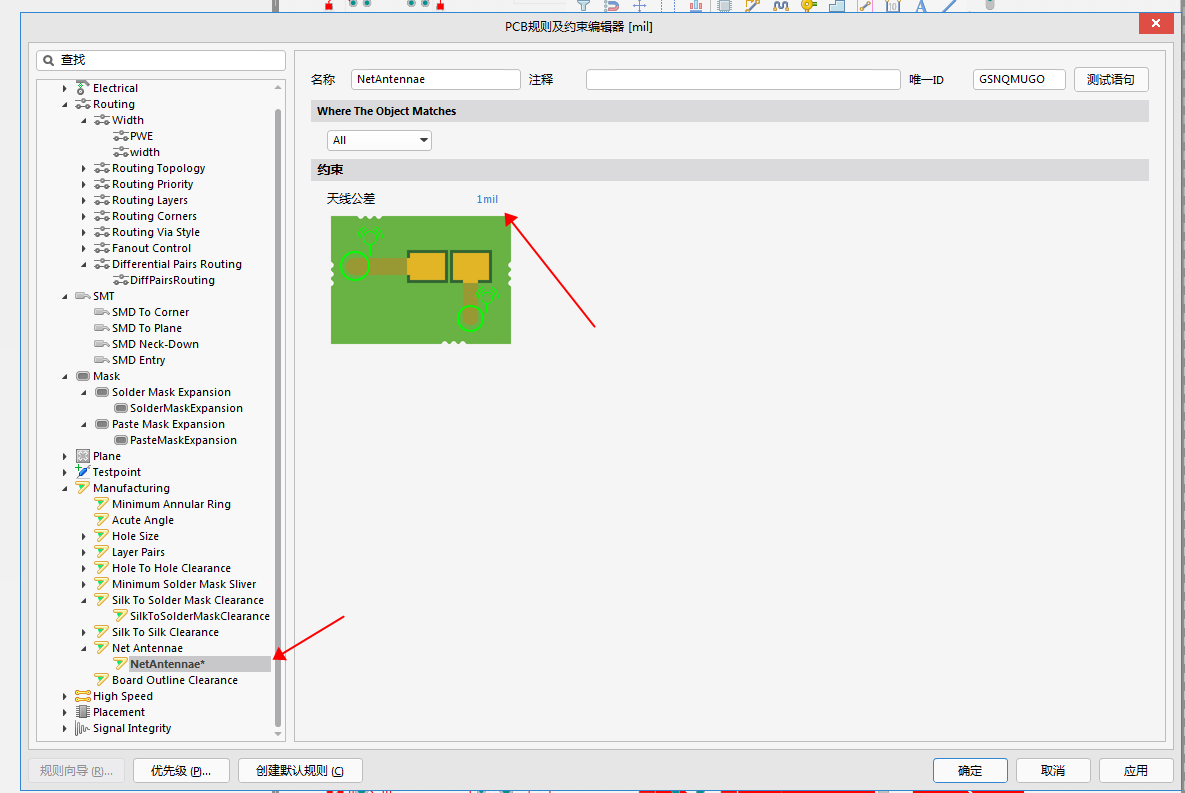

虽然可以对走线进行一些优化处理,但是考虑到还要人工进行布线处理,难免会对走线的一些线头有遗漏,这种线头简称Stub线头。Stub线头在信号传输过程中相当于一跟“天线”,不断地接受或发射电磁信号,特别是高速的时候,容易给走线导入串扰,所以有必要对Stub线头进行检查,并在设计中进行删除处理。

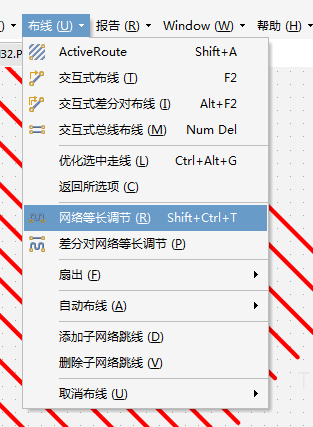

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

敷铜完整性的要求如图5-208与5-209所示,设计上保证主控下方敷铜的完整性及连续性,能够提供良好的信号回流路径,改善信号传输质量,提高产品的稳定性,同时也可以改善铜皮的散热性能。

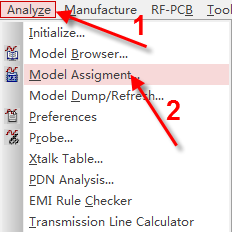

所谓的Xnet,是指在无源器件的两端,两个不同的网络,但是本质上其实是同一个网络的这种情况。比如一个源端串联电阻或者串容两端的网络。在实际设计情况中,我们需要对这种进行Xnet的设置,方便进行时序等长的设计,一般信号传输要求都是信号的传输总长度达到要求,而不是分段信号等长,这时采用Xnet就可以非常方便的实现这一功能,在Allegro软件中添加xnet的具体步骤如下所示:第一步,执行菜单命令Analyze-Model Assigment,进行模型的指定,如图5-112所示; 图5-11

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

此文从射频界面、小的期望信号、大的干扰信号、相邻频道的干扰信号以下几点解读射频电路四大基础性特性,并提供了在电路设计过程中都要非常注意的主要关键因素。 射频电路设计之射频的界面 无线发射器和接收器在基本概念上,可分成基频与射频两个部分。基频包含发射器的输入信号之频率范围之内,也包含接收器的输出信号之频率范围之内。基频的频宽影响了数据在系统中可流动的基本速率。基频是用于改善数据流的稳定度,并在特定的数据传输率之下,减少发射器产生在传输媒介的负荷量。 所以,电路设计基频电路时,都要更多的信号处

要点:1.高速PCB在设计中常见的问题;2.高速PCB的特殊材料要求;3.高速信号传输的特征和挑战4.高速PCB设计的原则和考虑因素5.PCB设计存在问题6.高速信号仿真分析工具有那些7.项目实例,高速PCB的信号完整性仿真办法和技巧

等长线是为了减少信号相对延时,常用在高速存储器的地址和数据线上,简单来说:等长线的作用,就是让信号传输的速度一致。在pads软件中只能在routet里面才能建立匹配长度的网络组,并进行等长的工作。

扫码关注

扫码关注