- 全部

- 默认排序

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

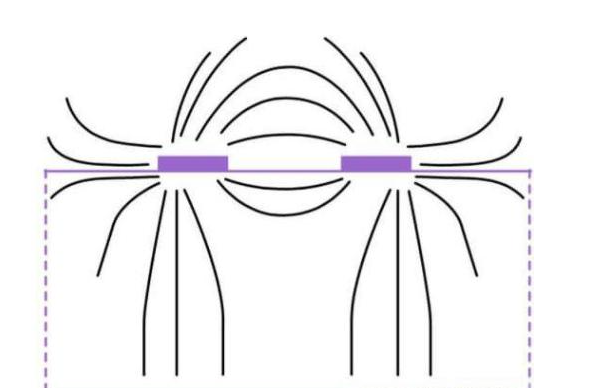

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。

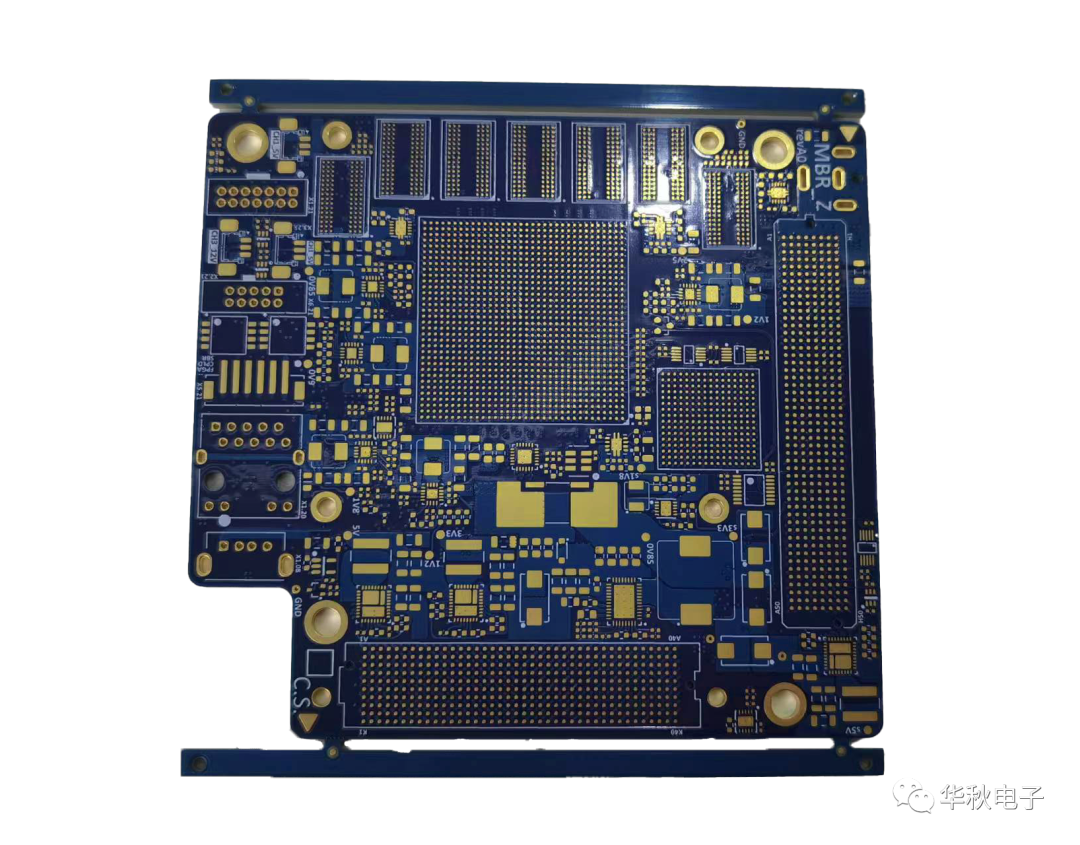

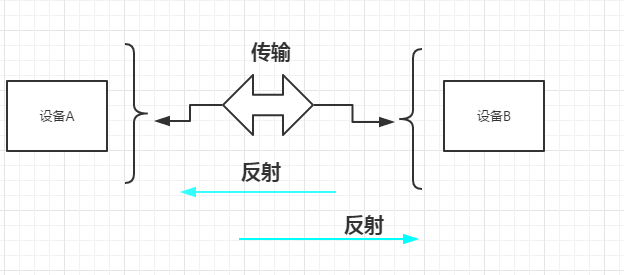

随着高频高速电子产品的快速发展,信号传输过程更容易出现反射、串扰等信号完整性问题,且频率越高、传输速率越快,信号损耗越严重,如何降低信号在传输过程中的损耗、保证信号完整性是高频高速PCB发展中的巨大挑战。在高速PCB设计中,阻抗匹配显得尤为

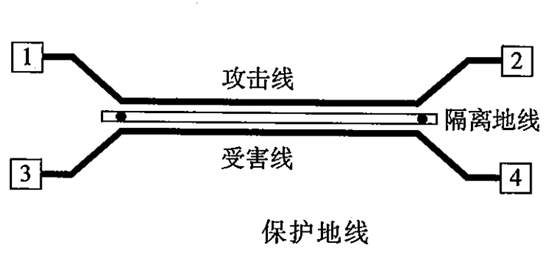

包地与串扰

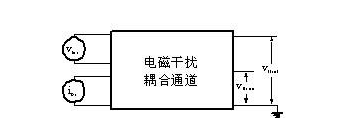

工程界常常使用保护地线进行隔离,来抑制信号间的相互干扰。的确,保护地线有时能够提高信号间的隔离度,但是保护地线并不是总是有效的,有时甚至反而会使干扰更加恶化。使用保护地线必须根据实际情况仔细分析,并认真处理。保护地线是指在两个信号线之间插入一根网络为GND的走线,用于将两个信号隔离开,地线两端打GN

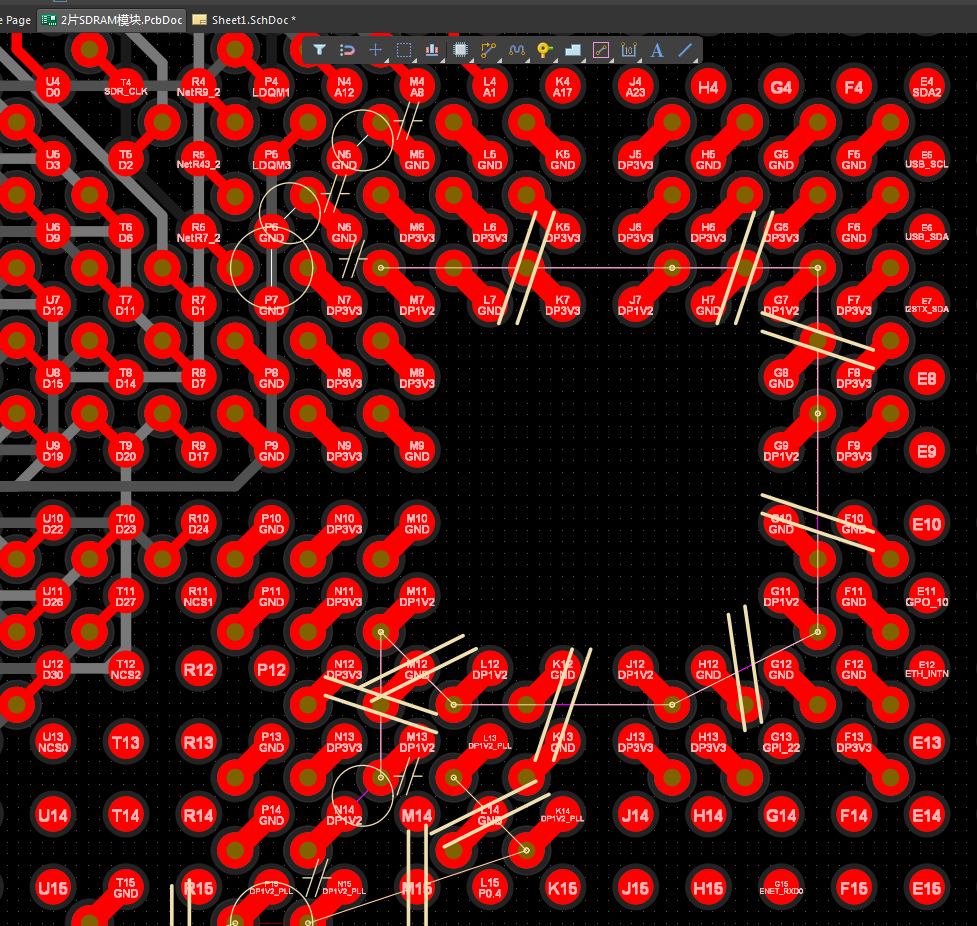

电源信号都没有处理:注意等长线的GAP尽量满足大于等于3W长度:可以减少串扰。注意看下xsignals分组 U16 -U17没有信号:数据跟地址用GND走线隔开:此处电源可以在电源层分割:以上评审报告来源于凡亿教育90天高速PCB特训班作业

在现代高速电子设备中,PCB板的阻抗测量和控制是至关重要的技术,准确的阻抗设计和测量可确保产品的信号完整性、抑制信号串扰及提高系统性能,因此是很多电子工程师的重点学习内容,下面聊聊PCB阻抗测量及控制方法。一、PCB板上如何测量阻抗?1、T

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

扫码关注

扫码关注