- 全部

- 默认排序

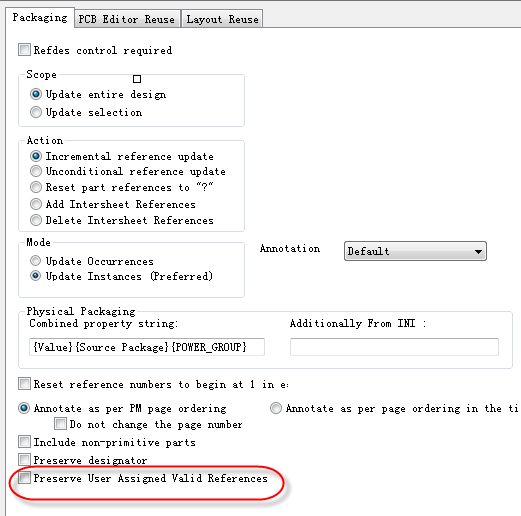

答:我们在使用Orcad软件进行原理图的绘制,会发现这样的一个问题,初始放置出来的器件的,器件编号是正常的,我们进行修改一下之后呢,器件编号下边就会出现一个下划线,这个下划线表示,我们这个器件编号是修改过的,做一个记号。这时候我们需要对整个设计文件中器件编号进行一个重新排列,而我们又想我们自己修改过的位号不进行改变,我们只需要在进行位号重新排列的时候,勾选上“Preserve User assigned Valid References”选项,则重排后此器件的编号不会改变,如图3-234所示:&

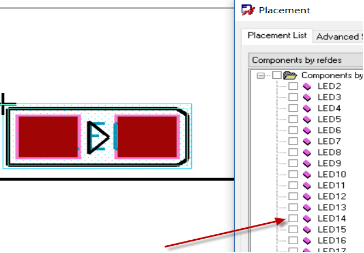

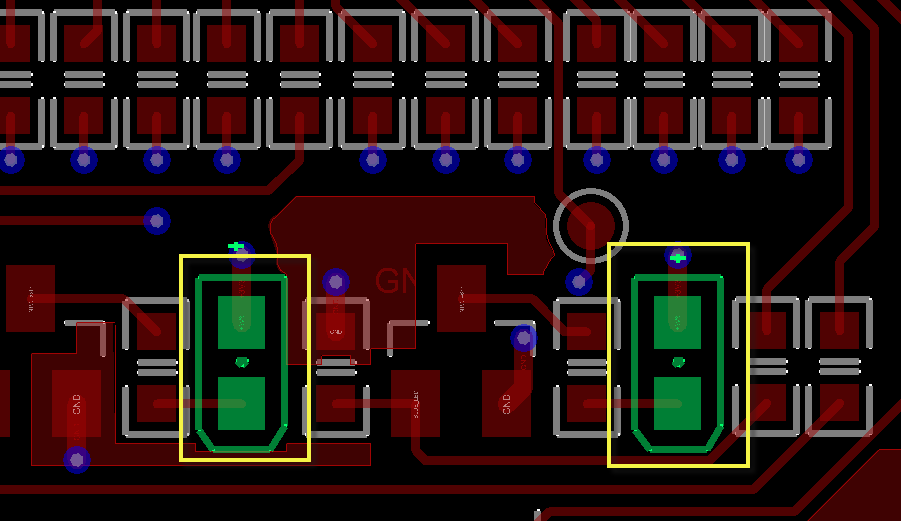

答:这里所说的assign RefDes功能,就是为复制的假的元器件进行编号的指定,一般用于LED灯板这类很多相同的模块的PCB板的设计中,具体操作的步骤如下所示:第一步,这些假的器件必须是要后台存在的,没有放置在PCB中,如图5-226所示;

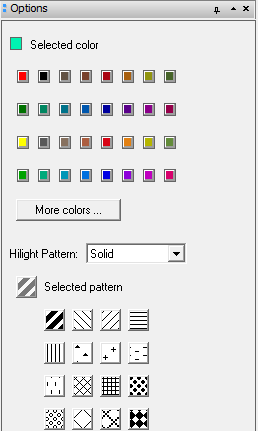

在PCB设计的时候,常常为了设计方便,会对某些特殊的网络或者某一网络类进行颜色的分配,具体步骤如下:1)给某一单独的网络进行颜色的分配执行菜单命令Display-assign Color,在Find面板上勾选网络,在Options面板中选择

答:高亮显示命令,也就是assign Color命令。在Allegro软件进行PCB设计的时候,是应用非常广泛的命令,如图5-76所示。这里我我们详细介绍一下,高亮显示的使用方法以及在Options参数面板的设置,具体如下:

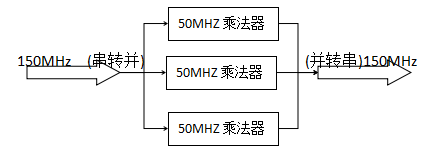

一、逻辑设计(1)组合逻辑设计下面是一些用Verilog进行组合逻辑设计时的一些注意事项:①组合逻辑可以得到两种常用的RTL 级描述方式。第一种是always 模块的触发事件为电平敏感信号列表;第二种就是用assign 关键字描述的数据流赋值语句。②always 模块的敏感表为电平敏感信号的电路可几

答:第一步,点击Display-assign Color选项,如图6-218所示;

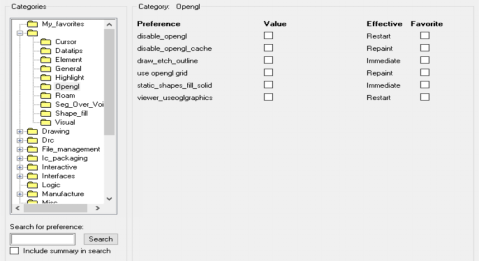

答:第一步,点击执行菜单命令Setup-User prefeences,进行用户设计属性的设置;第二步,执行命令之后,弹出如图5-229所示的界面,左侧边栏为常规设计参数的根目录,右侧边栏为常规设计参数的设置选项,具体的含义如下所示:

答:我们在使用16.6版本的Orcad软件绘制原理图的时候,会出现这样的情况,就是从库里面放置的元器件的编号是没有问题的,但是手动对这个元器件的编号进行修改之后呢,就会出现这个编号的下面会出现一个下划线,如图3-197所示,我们这里讲解下,怎么去掉这个元器件编号下面的下划线,具体的操作步骤如下: 图3-197 元器件编号下划线示意图第一步,选中有下划线的元器件,比如图3-198所示的C110这个器件,然后单击鼠标右键,在下拉的菜单中选择User assigned Refer

扫码关注

扫码关注