- 全部

- 默认排序

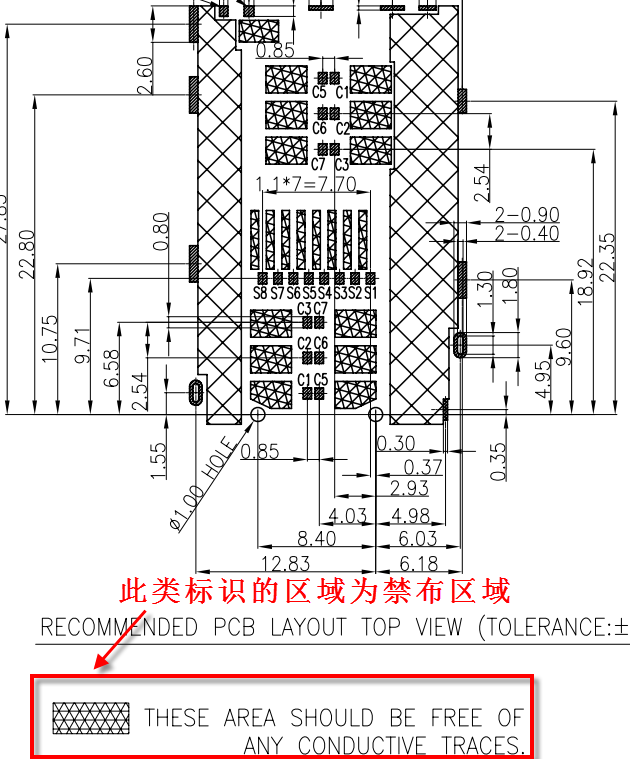

答:在PCB封装中,出现以下情况需要画Keepout层,一般绘制在Route Keepout、Via Keepout层。第一,如果Datasheet中指明了需要画Keepout层,则需要绘制Keepout层,绘制的大小按照Datasheet中指定的大小,如图4-122所示,

Product DescriptionDR 6018-S based on IPQ6010 chipset is an enterprise wireless module integrated with 2×2 5G high power

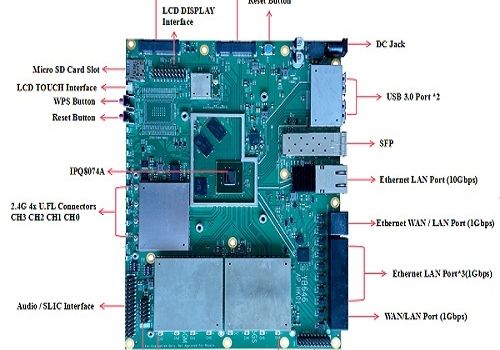

2x(4×4 or 8×8) 11AX MU-MIMO DUAL CONCURRENT EMBEDDEDBOARDIPQ8074A 4x4 2.4G 8x8 5G 802.11axDR8074A(HK01)2x(4×4 or 8×8) 11

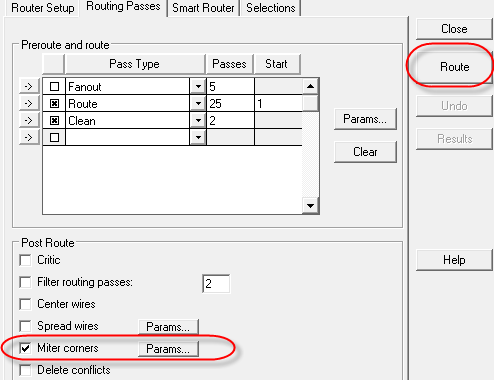

答:对于一些简单的,空间比较足的PCB,Allegro软件可以进行自动布线设计。第一步,将布线的线宽、间距规则设置好。点击Route-PCB Router-Route Automatic选项,如图6-305所示;

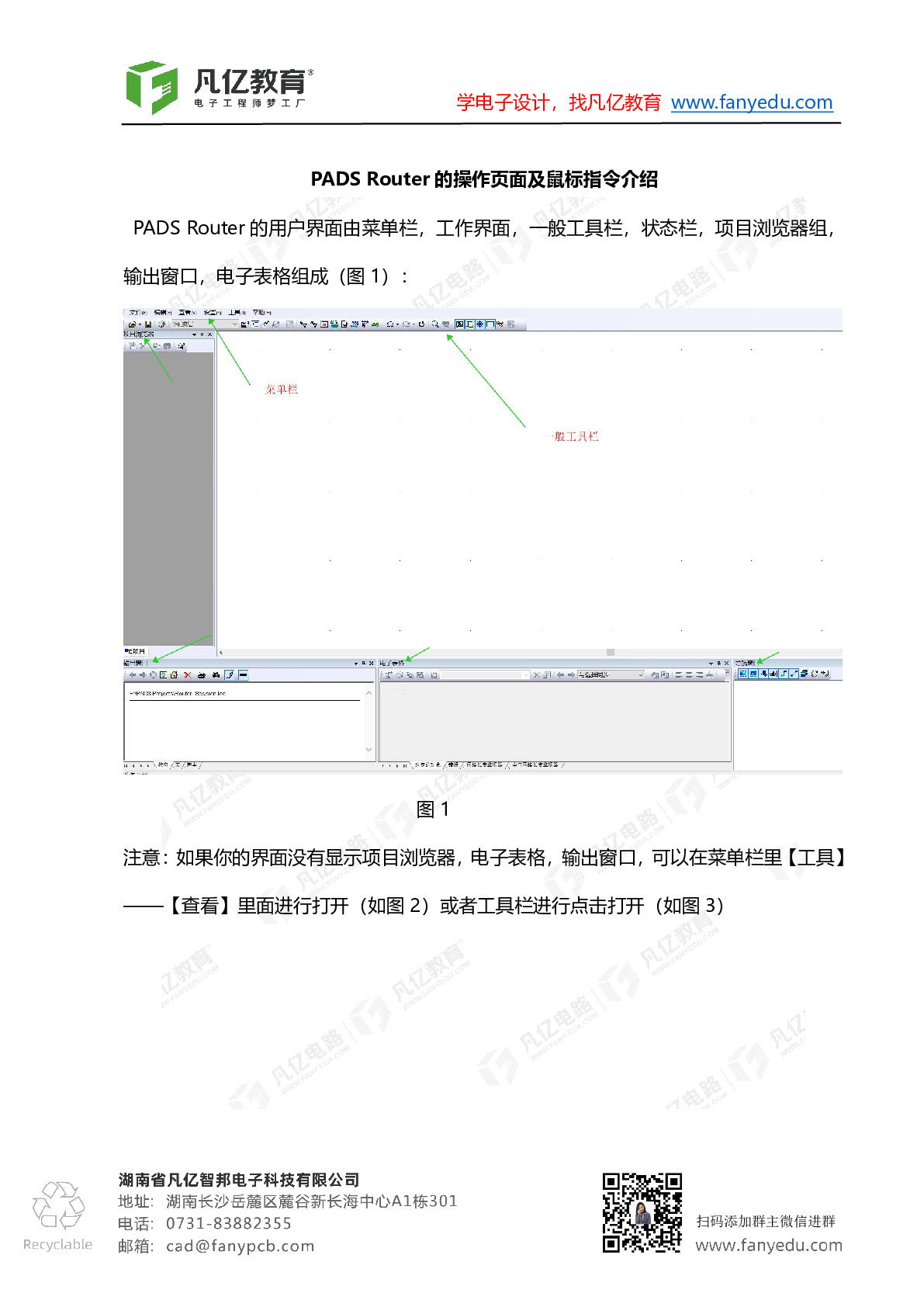

课程介绍:将采用PADS VX2.7,为了方便初学者也能直接看4层板的设计,PADS软件有三个组件,Logic、Layout、Router三个组件基本用法,分别对应原理图、布局、布线,按照PCB的流程决定从头开始讲,从项目整体介绍、原理图库

自动布线 为何出现Please select appropriate layer to Route.该怎么解决呢?

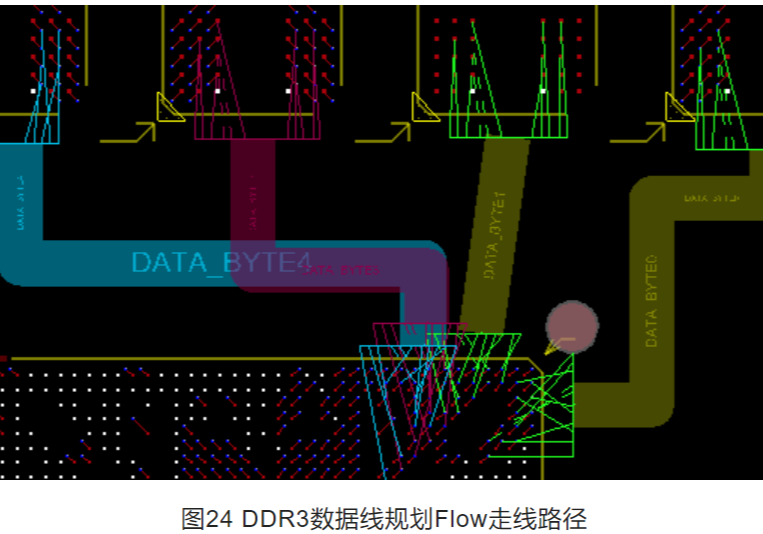

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

原理图绘制完成之后,需要对整个原理图的器件进行重新自动编号,之前pads 9.5是没有这个重新自动编号的功能,后面更新的版本添加了这个功能,这样更加方便了我们的设计。

扫码关注

扫码关注