- 全部

- 默认排序

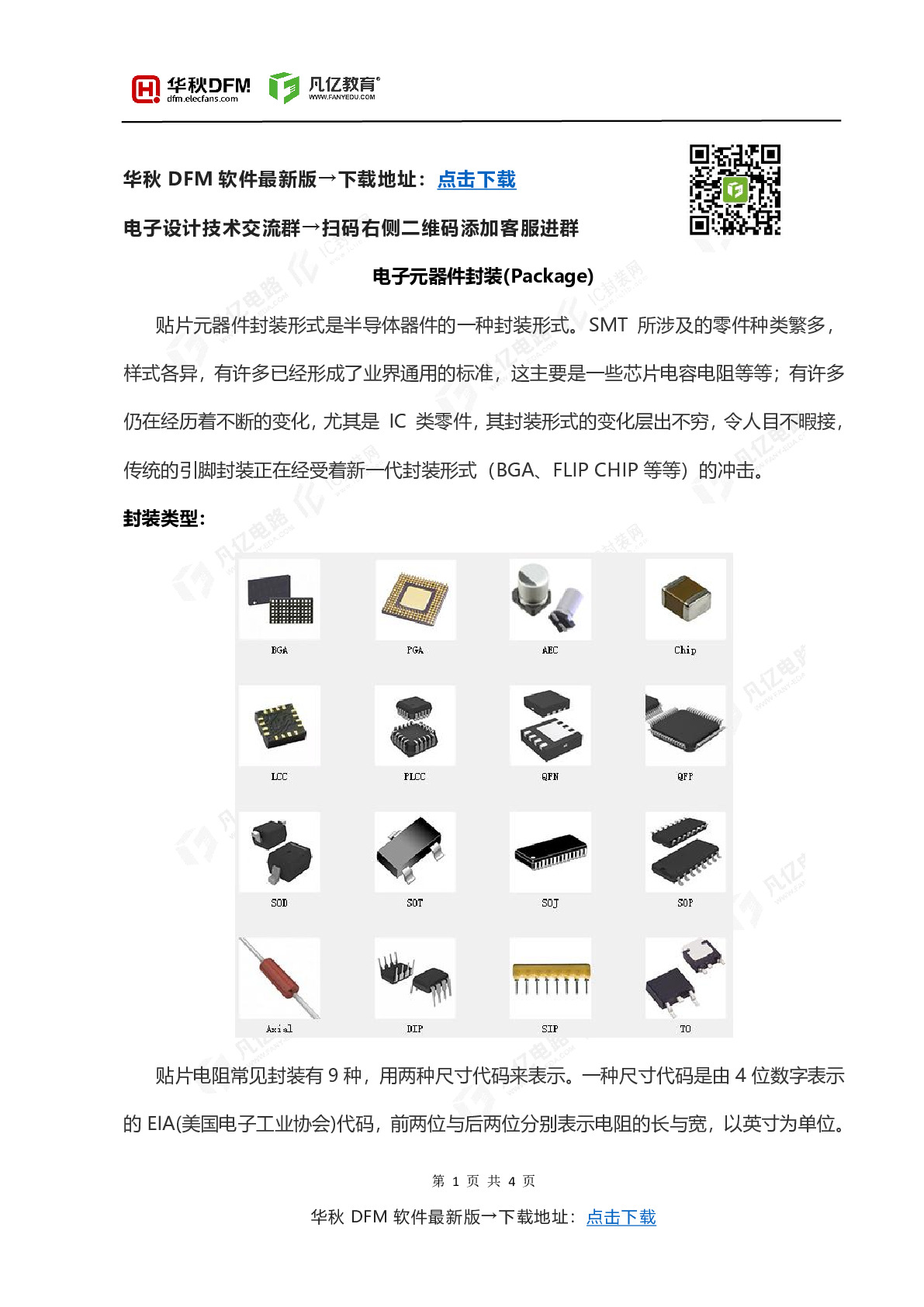

答:用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。一般放置占地面积是根据不同的器件类型放置不同尺寸大小,具体大小可参考以下尺寸。Chip元件, place_bound层器件最大外围尺寸(焊盘和丝印中取大值)

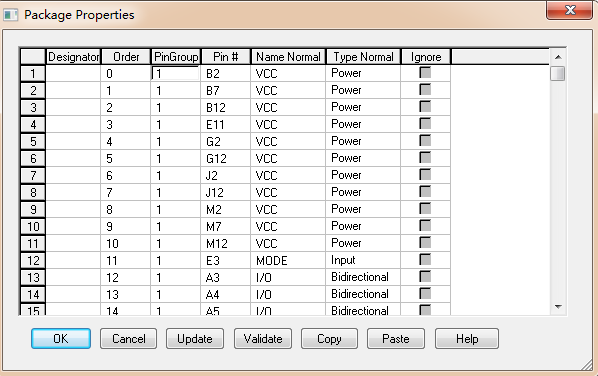

答:Pin Group这个属性是指可以交换的属性设置,我们删除这个属性的操作如下;第一步,打开库文件,点击菜单View→Package,进入到整个器件的编辑属性,然后点击菜单Edit→Properties,或者按快捷键Ctrl+E,进入器件管脚属性编辑页面,如图2-92所示: 图2-92 编辑器件属性示意图第二步,在弹出的器件属性框找到Pin Group这一栏,Pin Group这一栏中定义了数值,数值相同的就是可以进行管脚交换的,如图2-93所示; 图2-93&n

BGA 是 PCB 上常用的组件,通常 CPU、NORTH BRIDGE、SOUTH BRIDGE、AGP CHIP、CARD BUS CHIP…等,大多是以 bga 的型式包装,简言之,80﹪的高频信号及特殊信号将会由这类型的 Package 内拉出。因此,如何处理 BGA Package 的走线

有大神遇到过Package keepin层删不掉的情况吗?file:///一直显示Selected item not valid for current operation, ignored: Rectangle "Package Keepin/All"No valid items selected

17.4和17.2不一样吗?按照视频讲解的去做 按住ctrl 选中的管脚会拖动 而且我进入这个Package里面这个Package properties是无法点击的 也不像视频说的双击左键会出来 属性框

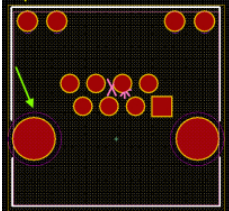

如图所示Package symbol里面是元件封装和3d图是这样放到board里就变成了这样请问各位是正常的么,这个孔可以正常使用或者给电么

用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的Shape,这个Shape表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。

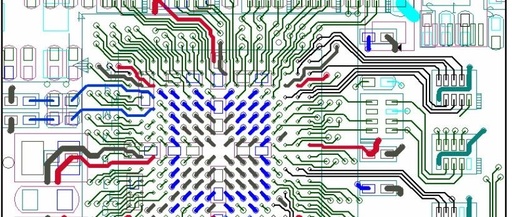

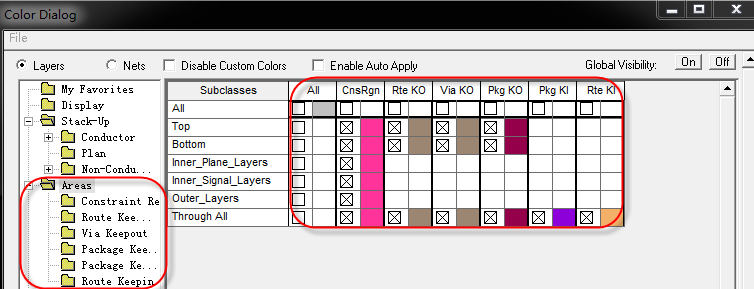

我们在进行PCB设计的时候,需要根据不同的PCB板结构以及一些电子产品的需求来进行各种不同区域的设计,包括允许布局区域设计、禁止布局区域设计。允许布线区域设计等等。在Allegro设计中,设置这些就在Areas,如图5-60所示。 图5-60 各类布局布线区域示意图Ø 在Allegro软件中有Route Keepout、Route Keepin、Package Keepout、Package Keepin、Via Keepout等多种类型的区域进行设置,对PCB工

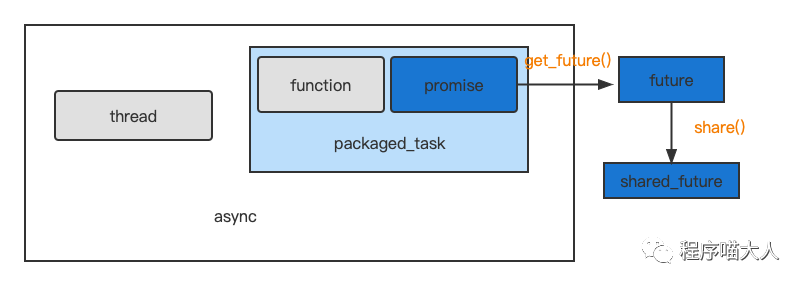

并发编程一般指多线程编程,C 11之后关于多线程编程有几个高级API:std::threadstd::futurestd::shared_futurestd::promisestd::Packaged_taskstd::async可能很多人都搞不清楚它们之前有什么联系,可以直接看这张图:如果连它们

扫码关注

扫码关注