- 全部

- 默认排序

在我们PCB设计中,板框很多时候都会是不规则的异形板框,可是在AD中并不能把它制作出来设置成为板框,这个时候我们就需要去从CAD中导入我们所需要的异形图形进来从而形成异形板框。

我们有时在进行PCB设计的时候,肯定会选择直接拖动 一个元器件或者一个模块去进行自己想要的布局。那么,就会遇到我们在拖动的时候,这个元器件或者这个模块是高亮,但是其它元器件与区域全部都是完全黑暗的,我们根本都看不清楚,此刻拖动的元器件或者模块被放置在哪里了,是不是重叠了其它的元器件放置。所以,遇到这个问题,我们应该如何解决呢?

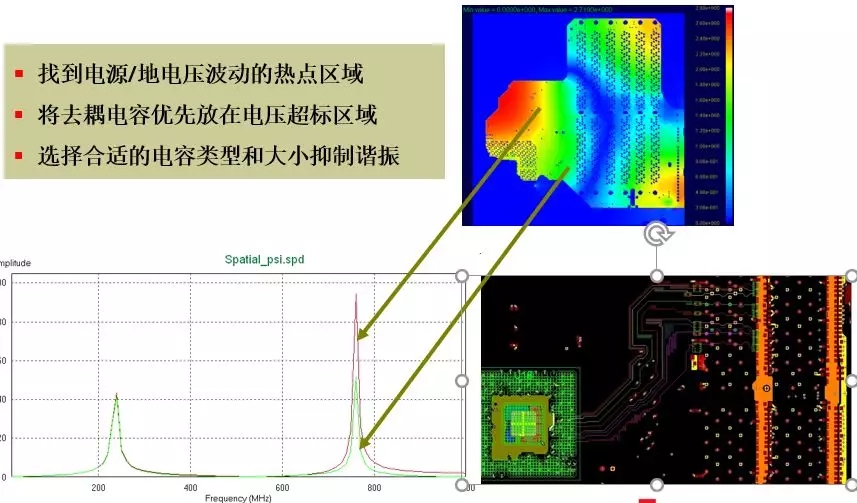

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

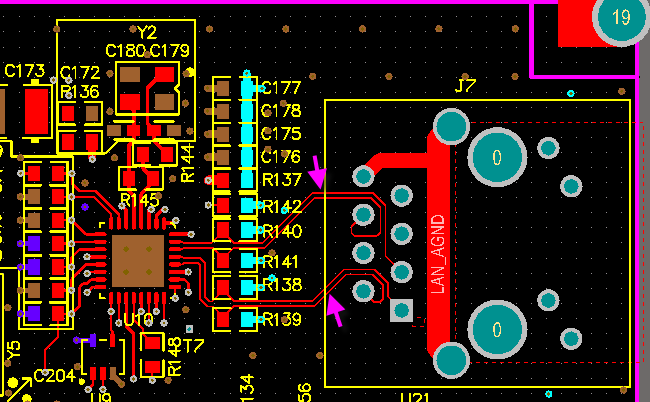

以太网(Ethernet)是一种计算机局域网组网技术,该技术基于IEEE制定的IEEE 802.3标准,它规定了包括物理层的连线、电信号和介质访问层协议的内容。 以太网是当前应用最普遍的局域网技术。Ethernet的接口是实质是MAC通过MII总线控制PHY的过程。

我们在用allegro进行PCB设计完成以后,都需要对一组传输的总线进行时序等长,在做时序等长的时候,分为绝对传输延迟与相对传输延迟。绝对传输延迟,顾名思义,信号传输在PCB设计中都是有一个走线的长度,我们通过设置这个信号线传输的最大值与最小值,来实现等长的方法,就称之为绝对传输延迟。

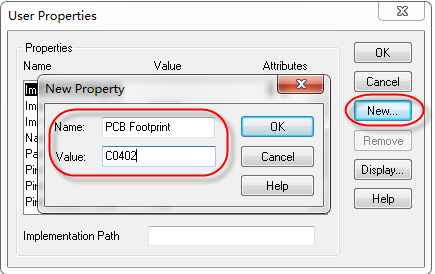

PCB设计:怎么显示与隐藏原理图库的PCB封装名称? 答:这里我们分为两种情况进行分析,一种是在绘制原理图库的时候,怎么显示与隐藏元器件封装名称;另外一种是在绘制原理图的时候,怎么显示与隐藏元器件封装名称。 ① 绘制原理图库时隐藏PCB封装的操作步骤如下; 第一步,打开所要隐藏PCB封装名的库文件,点击菜单Options→Part Properties编辑属性;

深圳晶振电路的PCB设计

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。 我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电极上施加电场会使晶体产生机械变形,反之,如果在晶体两侧施加机械压力就会在晶体上产生电场。并且,这两种现象是可逆的。利用这种特性,在晶体的两侧施加交变电压,晶片就会产生机械振动,同时产生交变电场。这种震

下单后扫码助教老师拉入特训营群学习添加时备注:20天一、本课题开设目的:本视频教学以免费的国产EDA工具-嘉立创EDA专业版为平台,以嘉立创官方设计的开发板“梁山派”为案例,来讲解一个四层板子的设计,之前很多电子工程师的画板一般停留在2层板

扫码关注

扫码关注