- 全部

- 默认排序

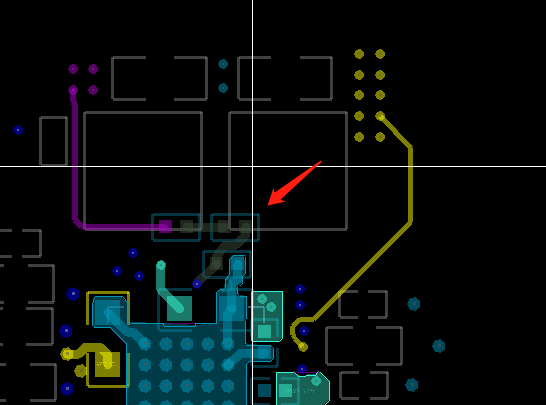

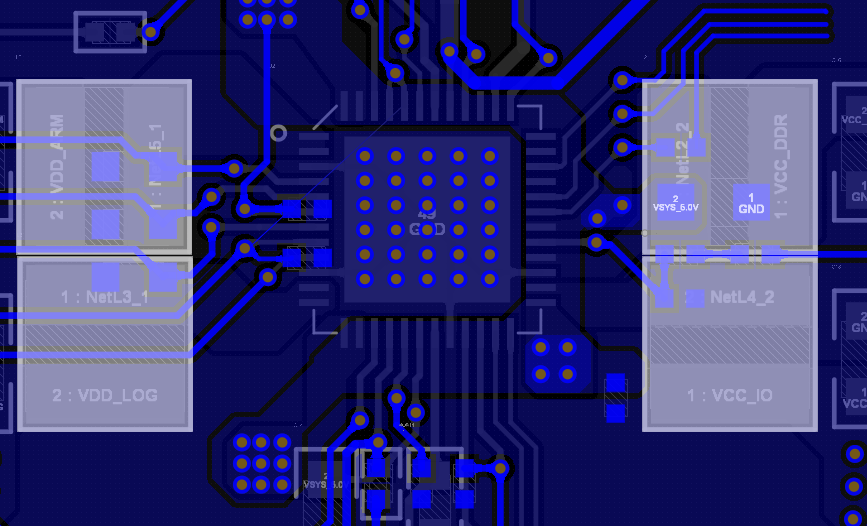

电感下面不要放置器件,自己优化下:此处DCDC5.0V输入建议铺铜处理以满足载流大小,或者加粗走线的宽度能满足:此处存在铜皮瓶颈处,自己优化下:此处LDO电路中的电源信号能顶层连接的,就把过孔删掉:存在多处情况。右边的LDO电源信号存在上述

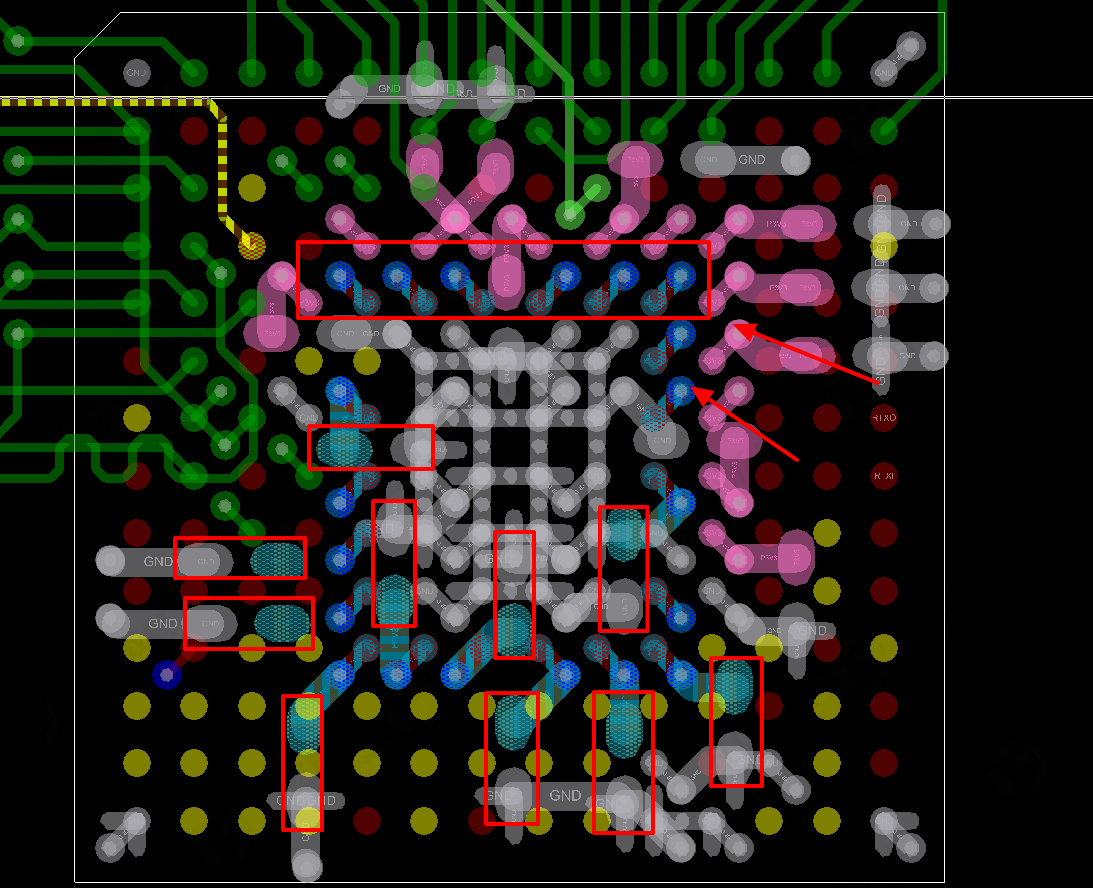

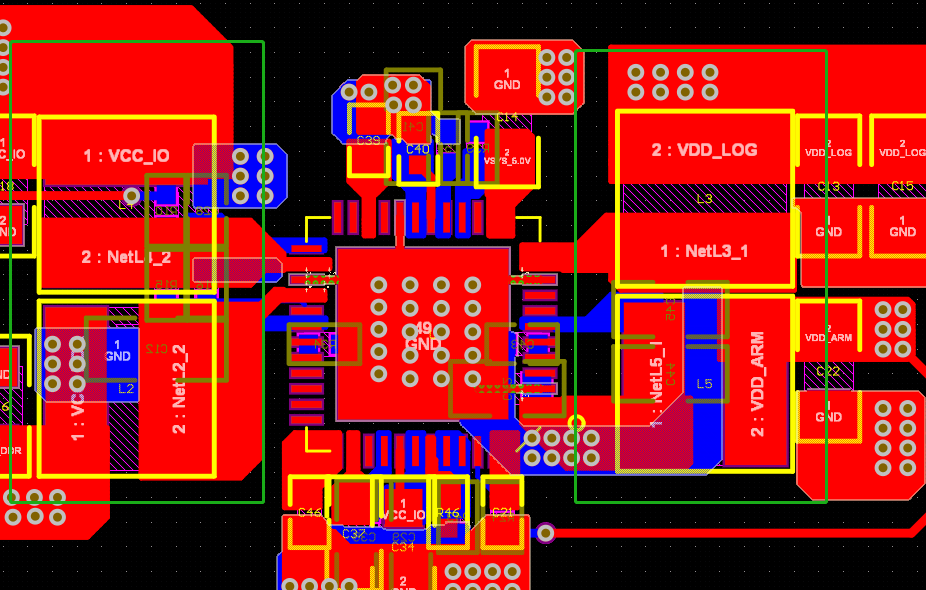

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

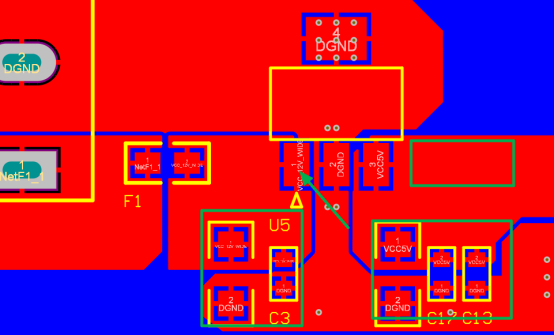

此处DCDC5.0V线宽满足不了载流:电感内部放置铜皮挖空区域,进行内部挖空:注意LDO电源的器件尽量整体中心对齐下:扇孔注意下对齐:看下此处的VCC-IO线宽是否能满足载流:器件注意对齐:以上评审报告来源于凡亿教育90天高速PCB特训班作

AP1236 是一款高精度,底噪声,CMOS LDO稳压器。AP1236提供底输出噪声,高波纹抑制率,底DROPOUT和非常快的开机时间,是当今前沿手机的理想选择。AP1236内部包括一个参考电原谅源,误差放大器,驱动晶体管,电流限制品和相

招聘岗位:FPGA开发工程师1位,要求电子,计算机相关专业,目前主要使用的是Altera FPGA。 公司简介:芯天下技术股份有限公司是一家芯片设计公司,主要的芯片有NOR和NAND存储器,MCU,LDO等电源管理芯片,公司20年销售额有4亿多,目前公司有将近200人。

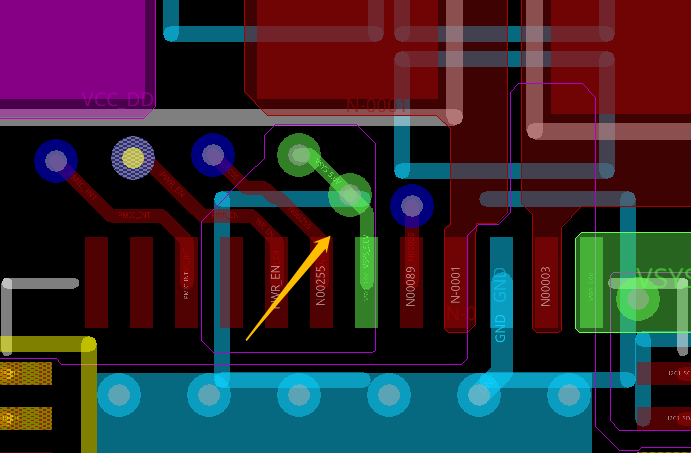

电容应靠近管脚放置,电流要先经过电容在到U5在到输出电容 电源十字连接处载流不够,手动加宽载流 地网络焊盘应靠近焊盘多打过孔 布局应呈一字型中心对齐放置器件,尽量做的整齐对称以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解P

LDO应用要点

(1) VRF滤波由LDO的工作原理可知,Vref(基准电压)的稳定性与LDO输出电源的纹波及噪声密切相关。为了减小器件面积,某些LDO在片内不提供对VREF引脚的滤波。在这种情下,设计者需在VREF引脚附近添加10uF电容,以保证VREF的低噪声和低纹波(2) SENSE(感应)引脚的处理SENSE引脚是LDO、DCDC电源芯片上常见的引脚在PCB上,当电源输出端与负载端相距较远时,输出电源Vout需通过较长距离的PCB导线(或PCB铜皮)才能加载到负载上,由于负载电流流经

注意电感底部不要放置器件以及走线,底部的器件爱你可以往IC下面塞,整体布局还需要更改:注意绘制铜皮不要存在直角:铜皮尽量宽度均匀点,优化下:看下LDO输入的载流大小是多少,按照比例计算对应的线宽要多少满足载流,注意加粗线宽:焊盘扇孔进来调整

电感器件下面不要放置器件以及走线,自己重新处理下布局,可以塞到IC下方:DCDC5V电源信号完全没有处理:铜皮尽量不要直角:电感内部注意挖空:打孔到焊盘上:顶层5V电源都没处理:不要从电感内部走线:LDO电源信号电流比较小,加粗走线就可以了

扫码关注

扫码关注