- 全部

- 默认排序

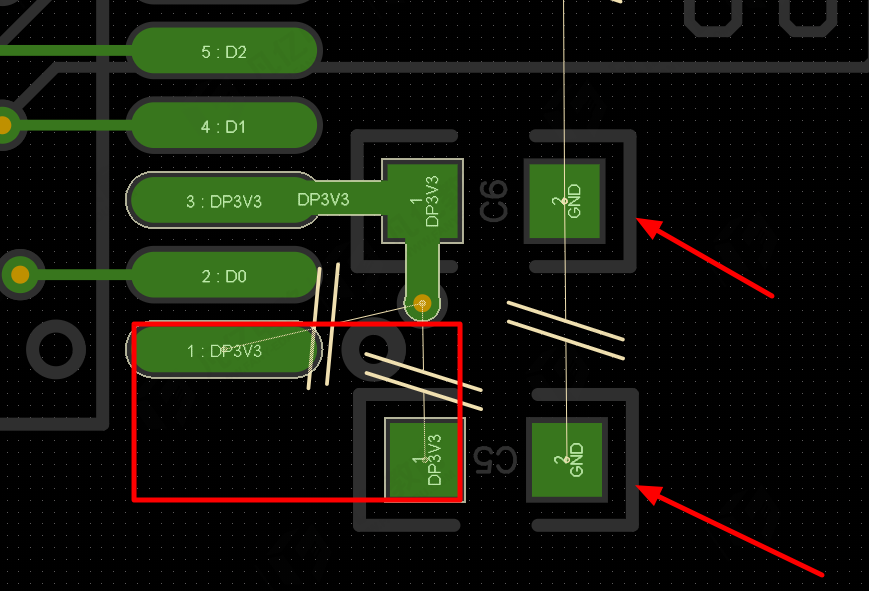

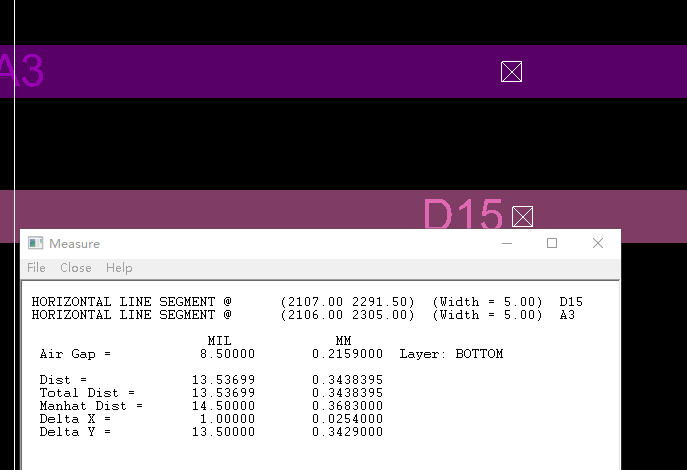

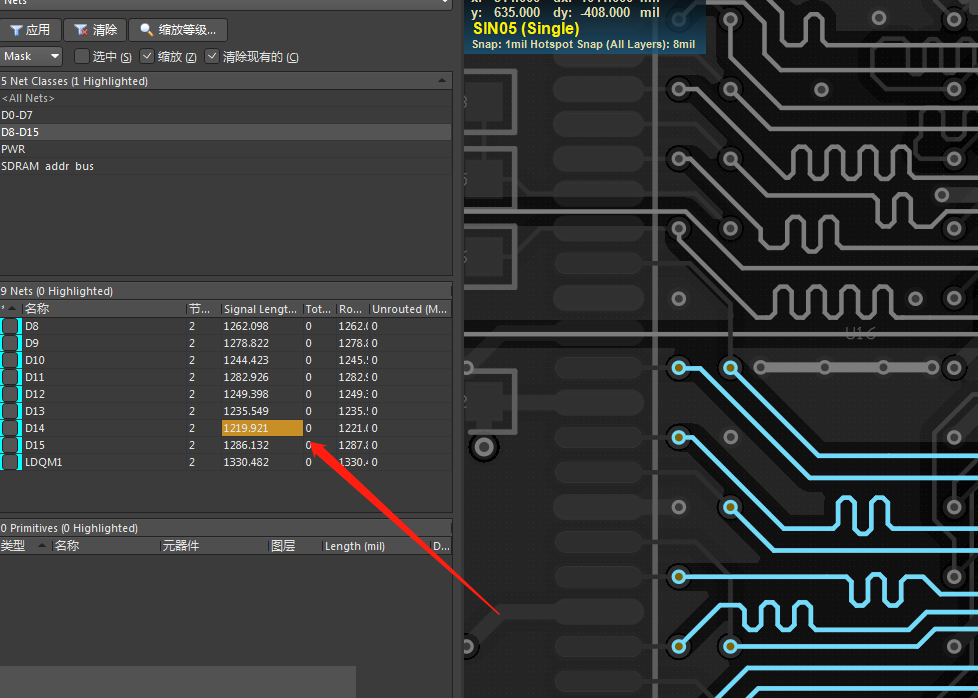

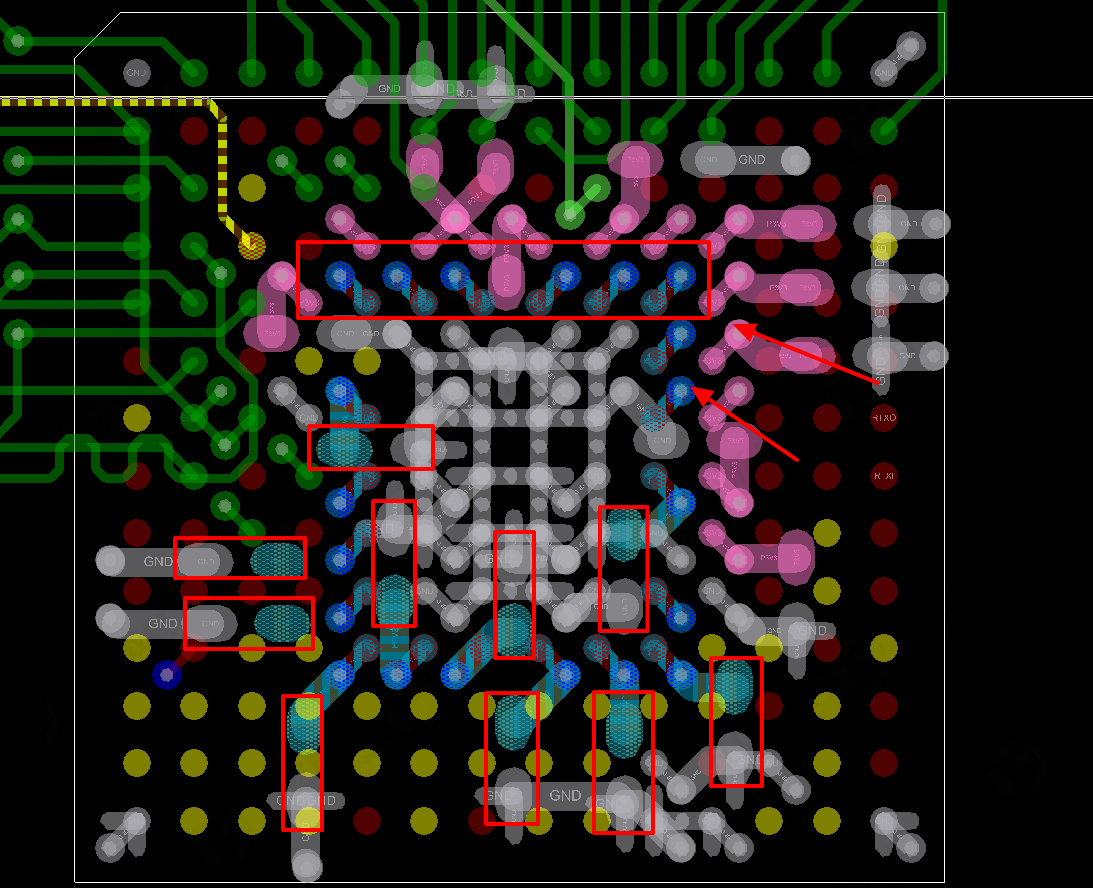

1.电源存在开路,地焊盘很多没有打孔造成开路报错。2.1v2电源过孔没有连通,造成天线报错。3.电源扇孔走线没有加粗4.时钟线电容应该考近芯片摆放5.时钟线等长错误,应与地址线放一组一起等长。6.地址线分组错误,缺少部分信号7.地址线等长错

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

2022年或许是DRAM内存多灾多难的一年,不仅迎来价格暴跌现象,还迎来了库存积压严重现象。毫不夸张地说,今年是DRAM内存大降价的一年。据市场调研机构数据报告显示,受到用户需求下滑影响,DRAM的价格在近两个月内严重下滑,下滑幅度将近20

随着电子技术高速发展,新技术及新概念层出不穷,如果了解过2022-2023年智能手机行业,很容易发现,那段时期的智能手机基本上是支持大内存,几乎所有顶配手机都有24GB、1TB等配置,这是因为内存迎来大降价,导致大内存成本很低,但现在这个状

信号线不满足3w间距数据线和地址线之间最好画一条加粗的gnd间隔开来以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm

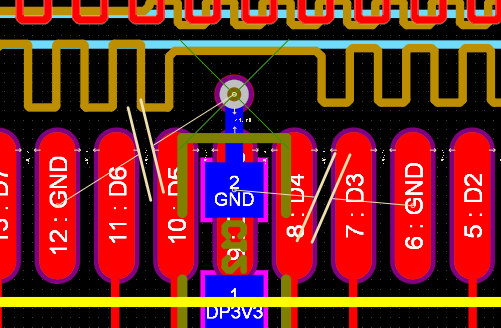

组内等长误差还存在报错:自己注意修改下等长,让组内误差没有报错。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;Ø DDR, Dual Data Rate双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM,人们习惯称

扫码关注

扫码关注